### NATIONAL UNIVERSITY OF SINGAPORE

### **CS2100 – COMPUTER ORGANISATION**

(Semester 2: AY2017/18)

Time Allowed: 2 Hours

### **INSTRUCTIONS TO CANDIDATES**

- 1. This assessment paper consists of **SEVEN (7)** questions and comprises **FOURTEEN (14)** printed pages.

- 2. This is a **CLOSED BOOK** assessment. One double-sided A4 reference sheet is allowed.

- 3. Calculators and computing devices such as laptops and PDAs are not allowed.

- 4. Answer all questions and write your answers in the **ANSWER BOOKLET** provided.

- 5. Fill in your Student Number <u>clearly with a pen</u> on your ANSWER BOOKLET.

- 6. Do <u>NOT</u> write your name on your ANSWER BOOKLET.

- 7. You may use pencil to write your answers.

- 8. Page 9 onwards contain a blank page, the MIPS Reference Data Sheet and several blank tables for your rough works.

- 9. You are to submit only the **ANSWER BOOKLET** and no other document.

- 1. [10 marks]

- (a) Write the output of the following C program.

[4 marks]

```

#include <stdio.h>

typedef struct {

int val;

char ch[2];

} rec t;

void process1(rec t *);

void process2(rec t);

int main(void) {

rec t st[2] = {\{11, \{'A', 'B'\}\}, \{22, \{'C', 'D'\}\}\};

process1(&st[1]);

process2(st[0]);

printf("%d %c\n", st[0].val, st[0].ch[0]);

printf("%d %c\n", st[1].val, st[1].ch[1]);

return 0;

}

void process1(rec_t *para) {

para -> val = 33;

para->ch[0] += ('a' - 'A') + 1;

para->ch[1] += ('a' - 'A') + 2;

}

void process2(rec_t para) {

para.val = 44;

para.ch[0] += ('a' - 'A') + 3;

para.ch[1] += ('a' - 'A') + 4;

}

```

(b) Given the following hexadecimal representation in IEEE 754 single-precision floating-point number system:

#### 42F64000

What is the decimal value it represents?

[3 marks]

- 1. (continue...)

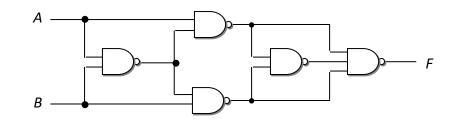

- (c) Given the logic circuit below:

- (i) What is F?

- [2 marks]

- (ii) What is the circuit propagation delay if the propagation delay of a NAND gate with fan-in of *n* is *nt*? [1 mark]

#### 2. [15 marks]

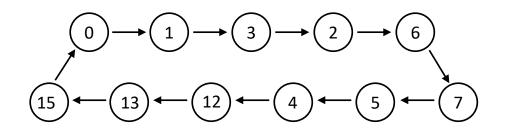

A sequential circuit goes through the following states, whose state values are shown in decimal:

The states are represented by 4-bit values *ABCD*. Implement the sequential circuit using a *D* flip-flop for *A*, a *D* flip-flop for *B*, a *T* flip-flop for *C*, and a *JK* flip-flop for *D*.

- a. Write out the **simplified SOP expressions** for all the flip-flop inputs. [10 marks]

- b. Implement your circuit according to your simplified SOP expressions obtained in part (a). Complete the given state diagram on the Answer Booklet, by indicating the next state for each of the five unused states. [5 marks]

#### 3. [20 marks]

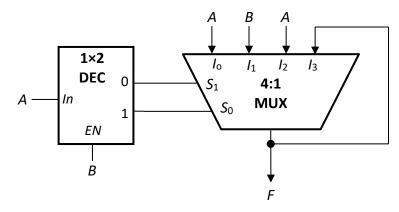

(a) Given the following circuit, what is *F*?

[4 marks]

- (b) Given  $G(A,B,C,D) = \prod M(1, 2, 6, 8, 9, 11, 13)$ , implement G using a single 8:1 multiplexer without any additional logic gates. Complemented literals are not available. [4 marks]

- (c) Given  $H(A,B,C,D) = \Sigma m(12, 13)$ , implement H using a single 2×4 active high output decoder with 1-enable, without any additional logic gates. Complemented literals are not available. [4 marks]

- (d) The BCD code (also known as 8421 code) values for the ten decimal digits are given below:

| Digit: | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|--------|------|------|------|------|------|------|------|------|------|------|

| Code:  | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

For example, the decimal value 396 is represented in BCD code as 0011 1001 0110.

Given two decimal digits A and B, represented by their BCD codes  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  respectively, implement a circuit without using any logic gates to calculate the BCD code of the 3-digit output of  $(51 \times A) + (20 \times (B\%2))$ , where % is the modulo operator. Name the outputs  $F_{11}F_{10}F_9F_8$   $F_7F_6F_5F_4$   $F_3F_2F_1F_0$ . You are free to use the logical constants 0 and 1.

For example, if A=2 (or 0010 in BCD) and B=7 (or 0111 in BCD), then  $(51\times A) + (20\times (B\% 2)) = 122$  or 0001 0010 0010 in BCD. Hence, the circuit is to produce the output 0001 0010 0010 for the inputs 0010 and 0111.

(*Hint:* To help you, you may fill in the table on the Answer Booklet that computes  $5 \times A$ . This table is worth 2 marks.)

[8 marks]

### 4. [12 marks]

- (a) Suppose MIPS instructions in R-format must use the following five opcodes (in decimal):

0, 1, 16, 17 and 32, what is the maximum total number of instructions that can be supported in MIPS?

- (b) Suppose due to a hardware defect in the datapath circuit, a stuck-at-0 fault occurs at **bit** 6 of every MIPS instruction. This means that bit 6 of a MIPS instruction is always 0 regardless of what the instruction is originally. Devise a simple test using a MIPS instruction to discover this error. Explain your test. Keep your explanation clear and short, in no more than 2 sentences. [3 marks]

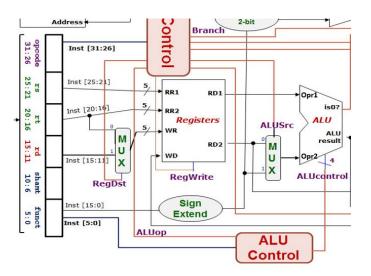

- (c) The diagram on the right shows a portion of the datapth.

Suppose the stuck-at-O fault occurs at the **ALUSrc** control signal. Assuming that **\$t0** and **\$t1** contains 12 and 34 respectively, and we are to use the instruction **Iw \$t1, 0(\$t0)** to discover the error. Describe what other preparation work needs to be done. You may assume that we can write data into any location in the memory. [3 marks]

(d) The table below shows the ALUcontrol signal of the datapath we discussed in class.

| Opcode | ALUop | Instruction operation | Funct<br>field | ALU action       | ALU<br>control |

|--------|-------|-----------------------|----------------|------------------|----------------|

| lw     | 00    | load word             | xxxxxx         | add              | 0010           |

| SW     | 00    | store word            | xxxxxx         | add              | 0010           |

| beq    | 01    | branch equal          | xxxxxx         | subtract         | 0110           |

| R-type | 10    | add                   | 100000         | add              | 0010           |

| R-type | 10    | subtract              | 100010         | subtract         | 0110           |

| R-type | 10    | AND                   | 100100         | AND              | 0000           |

| R-type | 10    | OR                    | 100101         | OR               | 0001           |

| R-type | 10    | set on less than      | 101010         | set on less than | 0111           |

You want to add the **bne** instruction into the datapath, which already includes the required hardware for the instruction. Write out the ALUop for **bne** and how you can determine whether the **bne** results in the branch to be taken. [4 marks]

#### 5. [15 marks]

Study the MIPS program below. *A* and *B* are integer arrays whose base addresses are in **\$s0** and **\$s1** respectively. The arrays are of the same size *n* (number of elements). **\$s2** contains the value *n*. The address of the first **beq** instruction is 0x0040003c.

```

# Q5.asm

.data

A: .word 11, 9, 31, 2, 9, 1, 6, 10

B: .word 3, 7, 2, 12, 11, 41, 19, 35

n: .word 8

.text

main: la

$s0, A

# $s0 is the base address of array A

$s1, B

la

# $s1 is the base address of array B

# $t0 is the addr of n (size of array)

la

$t0, n

# $s2 is the content of n

$s2, $zero, End

# Address: 0x0040003c

beq

addi $t8, $s2, -1

sll

$t8, $t8, 2

Loop: add $t0, $s0, $t8

$t1, $s1, $t8

add

lw

$t2, 0($t0)

$t3, 0($t1)

lw

andi $t4, $t3, 3

addi $t4, $t4, -3

beq $t4, $zero, A1

add

$t2, $t2, $t3

A2

j

A1:

addi $t2, $t2, 1

$t2, 0($t0)

A2:

รพ

addi $t8, $t8, -8

slt $t7, $t8, $zero

beq $t7, $zero, Loop

End:

li

$v0, 10

# system call code for exit

syscall

```

- a. Fill in the missing instruction (the fourth line in the program text) to store the value of *n* into **\$s2**. Do not use any pseudo-instruction. [1 mark]

- b. Fill in the values of array A after the execution of the code. [4 marks]

- c. Write an equivalent C code that does the same work. Use variables A and B for the arrays, and n for the size of the array. You do not need to declare A, B and n. [4 marks]

Give the instruction encoding in hexadecimal for the following 3 instructions:

| d. | sll | \$t8, \$t8, | 2 (Note: rs = 0) | [2 marks] |

|----|-----|-------------|------------------|-----------|

| e. | j   | A2          |                  | [2 marks] |

| f. | slt | \$t7, \$t8, | \$zero           | [2 marks] |

### 6. [14 marks]

Refer to the same MIPS code in the previous question, except that now we focus only on a section of the code which is reproduced below:

|       | beq  | \$s2, | \$zero, End         | # | Inst1  |

|-------|------|-------|---------------------|---|--------|

|       | addi | \$t8, | \$s2, -1            | # | Inst2  |

|       | sll  | \$t8, | \$t8, 2             | # | Inst3  |

| Loop: | add  | \$t0, | \$s0, \$t8          | # | Inst4  |

|       | add  | \$t1, | \$s1, \$t8          | # | Inst5  |

|       | lw   | \$t2, | 0(\$t0)             | # | Inst6  |

|       | lw   | \$t3, | 0(\$t1)             | # | Inst7  |

|       | andi | \$t4, | \$t3, 3             | # | Inst8  |

|       | addi | \$t4, | \$t4, -3            | # | Inst9  |

|       | beq  | \$t4, | \$zero, Al          | # | Inst10 |

|       | add  | \$t2, | \$t2, \$t3          | # | Inst11 |

|       | j    | A2    |                     | # | Inst12 |

| A1:   | addi | \$t2, | \$t2, 1             | # | Inst13 |

| A2:   | SW   | \$t2, | 0(\$t0)             | # | Inst14 |

|       | addi | \$t8, | \$t8, -8            | # | Inst15 |

|       | slt  | \$t7, | \$t8, \$zero        | # | Inst16 |

|       | beq  | \$t7, | \$zero, <i>Loop</i> | # | Inst17 |

| End:  |      |       |                     |   |        |

Assuming a 5-stage MIPS pipeline system with forwarding and early branching, that is, the branch decision is made at the ID stage. No branch prediction is made and no delayed branching is used. For the jump (j) instruction, the computation of the target address to jump to is done at the ID stage as well.

Assume also that the first **beq** instruction begins at cycle 1.

- a. Suppose arrays A and B now each contains 200 positive integers. What is the minimum number and maximum number of instructions executed? (Consider only the above code segment from Inst1 to Inst17.) [2 marks]

- b. List out the instructions where some stall cycle(s) are inserted in executing that instruction in the pipeline. These include delay caused by data dependency and control hazard. You may write the instruction number InstX instead of writing out the instruction in full.

- c. How many cycles does one iteration of the loop (from Inst1 to Inst17) take if the **beq** instruction at Inst10 branches to A1? You have to count until the WB stage of Inst17.

[3 marks]

- d. How many cycles does one iteration of the loop (from Inst1 to Inst17) take if the **beq** instruction at Inst10 does not branch to A1? You have to count until the WB stage of Inst17.

[3 marks]

#### 7. [14 marks]

Refer to the same MIPS code in the previous two questions:

| -     |      |       |                     |   |        |          |            |

|-------|------|-------|---------------------|---|--------|----------|------------|

|       | beq  | \$s2, | \$zero, <i>End</i>  | # | Inst1, | Address: | 0x0040003c |

|       | addi | \$t8, | \$s2, -1            | # | Inst2  |          |            |

|       | sll  | \$t8, | \$t8, 2             | # | Inst3  |          |            |

| Loop: | add  | \$t0, | \$s0, \$t8          | # | Inst4  |          |            |

|       | add  | \$t1, | \$s1, \$t8          | # | Inst5  |          |            |

|       | lw   | \$t2, | 0(\$t0)             | # | Inst6  |          |            |

|       | lw   | \$t3, | 0(\$t1)             | # | Inst7  |          |            |

|       | andi | \$t4, | \$t3, 3             | # | Inst8  |          |            |

|       | addi | \$t4, | \$t4, -3            | # | Inst9  |          |            |

|       | beq  | \$t4, | \$zero, Al          | # | Inst10 |          |            |

|       | add  | \$t2, | \$t2, \$t3          | # | Inst11 |          |            |

|       | j    | A2    |                     | # | Inst12 |          |            |

| A1:   | addi | \$t2, | \$t2, 1             | # | Inst13 |          |            |

| A2:   | SW   | \$t2, | 0(\$t0)             | # | Inst14 |          |            |

|       | addi | \$t8, | \$t8, -8            | # | Inst15 |          |            |

|       | slt  | \$t7, | \$t8, \$zero        | # | Inst16 |          |            |

|       | beq  | \$t7, | \$zero, <i>Loop</i> | # | Inst17 |          |            |

| End:  |      |       |                     |   |        |          |            |

Assuming that arrays A and B now each contains <u>1024</u> positive integers. Given a **direct-mapped data cache** with 128 words in total, each block containing 4 words with each word being 4 bytes long, arrays A and B are stored starting at memory addresses <u>0x10001000</u> and <u>0x1003F100</u> respectively.

The data cache is involved when memory is accessed (that is, when **Iw** and **sw** instructions are executed).

- a. How many bits are there in the index field? In the byte offset field? [2 marks]

- b. Which index is A[1023] mapped to? Which index is B[1023] mapped to? [4 marks]

- c. How many memory accesses in total are made for array A? For array B? [2 marks]

- d. What is the cache hit rate for array A? For array B? [2 marks]

- e. Given a direct-mapped instruction cache with 16 words in total, each block containing 2 instructions (words), and the first beq instruction is at memory address 0x0040003c. How many cache hits and misses are there in total during the execution of the code, assuming that the beq instruction at Inst10 always branches to A1? You may consider only the instructions in the given code segment, that is, Inst1 through Inst17.

~~ END OF PAPER ~~~

(The next few pages contain the MIPS Reference Data sheet, blank truth tables, K-maps and pipeline charts.)

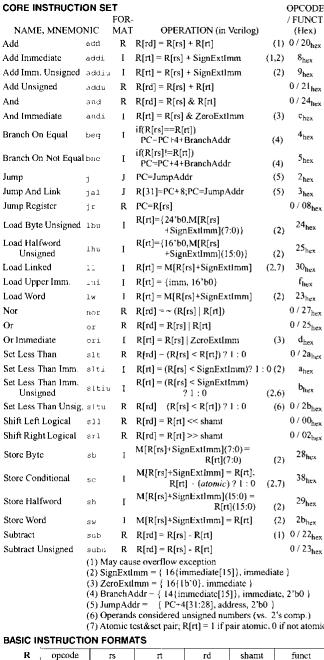

# MIPS Reference Data

(1)

| opcode | rs | rt    |       | rd | shamt  | funct |

|--------|----|-------|-------|----|--------|-------|

| 26     | 15 | 21 20 | 16 15 | 11 | 10     | 6.5   |

| opcode | rs | rt    | i     |    | immedi | ate   |

| 26     | 25 | 21 20 | 16 15 |    |        |       |

1 J

| ARITHMETIC CORE               | INSTRU | e e e                                                            | OPCODE               |

|-------------------------------|--------|------------------------------------------------------------------|----------------------|

|                               | FOR    |                                                                  | / FMT /FT<br>/ FUNCT |

| NAME, MNEMONIC                |        |                                                                  | (Hex)                |

| Branch On FP True bet         |        | if(FPcond)PC=PC+4+BranchAddr (4)                                 | 11/8/1/              |

| Branch On FP False bel        |        | if(!FPcond)PC=PC+4+BranchAddr(4)                                 | 11/8/0/              |

| Divide di                     | v R    | Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt]                                   | 0//-1a               |

| Divide Unsigned div           | vu R   | Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt] (6)                               | 0///1b               |

| FPAdd Single add              | .s FR  | F[fd] = F[fs] + F[ft]                                            | 11/10//0             |

| FP Add                        | .d FR  | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} +$                            | 11/11//0             |

| Double add                    | .a rĸ  | { <b>F</b> [ <b>f</b> t], <b>F</b> [ <b>f</b> t+1]}              | 11/11//0             |

| FP Compare Single c.x.        | s• FR  | FPcond = (F[fs] op F[ft])?1:0                                    | 11/10//y             |

| FP Compare                    | d• FR  | $FPcond = (\{F[fs], F[fs+1]\} op$                                | 11/11//y             |

| Double                        |        | (F[ft],F[ft+1]))? 1:0                                            | 11/1009              |

|                               |        | ==, <, or $<=) (y is 32, 3c, or 3c)$                             |                      |

| FP Divide Single div          | .s FR  | F[fd] = F[fs] / F[ft]                                            | 11/10//3             |

| FP Divide                     | .d FR  | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} /$                            | 11/11//3             |

| Double                        |        | {F[ft],F[ft+1]}                                                  |                      |

| FP Multiply Single mul        | .s FR  | F[fd] = F[fs] * F[ft]                                            | 11/10//2             |

| FP Multiply au1               | .d FR  | $\{F[fd],F[fd+1]\} = \{F[fs],F[fs+1]\} *$                        | 11/11//2             |

| Double                        | 50     | $\{F[ft],F[ft+1]\}$                                              | 11/10/ /1            |

| FP Subtract Single sub        | .s FR  | F[fd]=F[fs] - F[ft]                                              | 11/10//1             |

| FP Subtract                   | .a FR  | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]}$                              | 11/11//1             |

| Double Load FP Single 1w      | =1 ]   | $\{F[ft],F[ft+1]\}$                                              | 31///                |

| Load FP Single 1wo<br>Load FP | 51 I   | F[rt]=M[R[rs]+SignExt[mm] (2)                                    | 31///                |

| Double 1de                    | 21 I   | F[rt]=M[R[rs]+SignExtInim]; (2)<br>F[rt+1]=M[R[rs]+SignExtImm+4] | 35///                |

| Move From Hi mfl              | ni R   | R[rd] = Hi                                                       | 0 ///10              |

| Move From Lo mf:              |        | R[rd] = Lo                                                       | 0///12               |

| Move From Control mf          |        | R[rd] = CR[rs]                                                   | 10 /0//0             |

| Multiply mut                  |        | (Hi,Lo) = R[rs] * R[rt]                                          | 0///18               |

| Multiply Unsigned mul         |        | (H,Lo) = R[rs] * R[rt] (6)                                       | 0///19               |

| Shift Right Arith. sr         |        | R[rd] = R[rt] >> shamt                                           | 0///3                |

| Store FP Single sw            | -      | M[R[rs]+SignExtInim] = F[rt] (2)                                 | 39///                |

| Store FP                      |        | M[R[rs]+SignExtImm] = F[rt]; (2)                                 | 3d///                |

| Double                        |        |                                                                  |                      |

#### FLOATING-POINT INSTRUCTION FORMATS

| FR | opcode | fmt   | ft    | fs    | fd        | funct |

|----|--------|-------|-------|-------|-----------|-------|

|    | 31 26  | 25 21 | 20 16 | 15 11 | 10 6      | 5 0   |

| FI | opcode | fmt   | ft    |       | immediate | 2     |

|    | 31 26  | 25 21 | 20 16 | 15    |           | 0     |

PSEUDOINSTRUCTION SET

| 3 | SUDDING TRUCTION SET         |          |                                              |

|---|------------------------------|----------|----------------------------------------------|

|   | NAME                         | MNEMONIC | OPERATION                                    |

|   | Branch Less Than             | blt      | if(R[rs] <r[rt]) pc="Label&lt;/th"></r[rt])> |

|   | Branch Greater Than          | bgt      | if(R[rs]>R[rt]) PC = Label                   |

|   | Branch Less Than or Equal    | ble      | $if(R[rs] \le R[rt]) PC = Label$             |

|   | Branch Greater Than or Equal | bge      | $if(R[rs] \ge R[rt]) PC = Label$             |

|   | Load Immediate               | 11       | R[rd] = immediate                            |

|   | Move                         | move     | R[rd] = R[rs]                                |

|   |                              |          |                                              |

#### REGISTER NAME, NUMBER, USE, CALL CONVENTION

| NAME              | NUMBER | USE                                                      | PRESERVEDACROSS<br>A CALL? |

|-------------------|--------|----------------------------------------------------------|----------------------------|

| \$zero            | 0      | The Constant Value 0                                     | N.A.                       |

| \$at              | ]      | Assembler Temporary                                      | No                         |

| \$v0-\$vl         | 2-3    | Values for Function Results<br>and Expression Evaluation | No                         |

| \$a0-\$a3         | 4-7    | Arguments                                                | No                         |

| \$t0-\$t7         | 8-15   | Temporaries                                              | No                         |

| \$s0-\$s7         | 16-23  | Saved Temporaries                                        | Yes                        |

| \$t8-\$t9         | 24-25  | Temporaries                                              | No                         |

| <b>\$k0-\$k</b> 1 | 26-27  | Reserved for OS Kernel                                   | No                         |

| \$gp              | 28     | Global Pointer                                           | Yes                        |

| \$sp              | 29     | Stack Pointer                                            | Yes                        |

| \$fp              | 30     | Frame Pointer                                            | Yes                        |

| \$ra              | 31     | Return Address                                           | Yes                        |

Copyright 2009 by Elsevier, Inc., All rights reserved. From Patterson and Hennessy, Computer Organization and Design, 4th ed.

# (This page is for your rough work.)

DA

DB

KD

JD

|  | <br> | <br> |

|--|------|------|

|  |      |      |

|  |      |      |

|  |      |      |

|  | <br> | <br> |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  | <br> |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

|  |      |      |

# (This page is for your rough work.)

#### 1 2 2 3 4 5 5 6 7 0 1 3 4 beq addi sll add add lw lw andi addi beq A1 add JA2 A1: addi A2: sw addi slt beq

### (This page is for your rough work.)

|           | 1        | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 1<br>0 | 1<br>1 | 1<br>2 | 1<br>3 | 1<br>4 | 1<br>5 | 1<br>6 | 1<br>7 | 1<br>8 | 2<br>0 | 2<br>1 | 2<br>2 | 2<br>3 | 2<br>4 | 2<br>5 | 2<br>6 | 2<br>7 | 2<br>8 | 2<br>9 | 3<br>0   |

|-----------|----------|---|---|---|---|---|---|---|---|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------|

| 11        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| beq       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 12        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| addi      |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 13        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| sll       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 14        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| add       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 15        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| add       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 16        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| lw        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 17        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| lw        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 18        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| andi      | -        |   |   |   |   |   |   |   |   |        |        |        |        |        |        | -      |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 19        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| addi      | <u> </u> |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        | <u> </u> |

| 110       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| beq<br>A1 |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 111       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| add       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 112       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        | -      |        |        |        |        |        |        |        |        |        |        |        |        |          |

| J A2      |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 113       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| A1:       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| addi      |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 114       | 1        |   | 1 |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| A2:       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| sw        |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 115       | 1        |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| addi      |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 116       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| slt       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| 117       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

| beq       |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

|           |          |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |          |

|           | 1        |   |   |   |   |   |   |   |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        | 1        |

# (This page is for your rough work.)