CS2100 Computer Organisation Tutorial #8: MSI Components (Week 10: 25 – 29 March 2024) Answers to Selected Questions

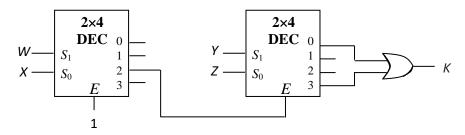

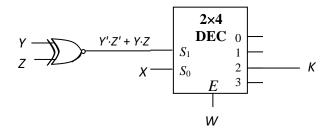

2. You are given the following Boolean function:  $K(W,X,Y,Z) = \Sigma m(8, 11)$ .

You are to implement this function using the fewest number of one-enabled 2×4 decoder with normal outputs and at most one logic gate? (Logic gates, as you have learned, are NOT, AND, OR, NAND, NOR, XOR, and XNOR.)

The following is one solution. Is there a simpler circuit using just one decoder and one logic gate?

Answer: There might be other answers.

3. [AY2011/2 Semester 2 Exam question]

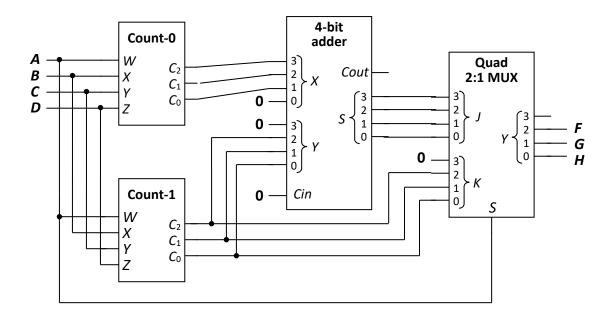

You are to design a converter that takes in 4-bit input *ABCD* and generates a 3-bit output *FGH* as shown in Table 1 below.

| Input   |   |   |   | Output |   |   |

|---------|---|---|---|--------|---|---|

| Α       | В | С | D | F      | G | Η |

| 0       | 0 | 0 | 0 | 0      | 0 | 0 |

| 1       | 0 | 0 | 0 | 0      | 0 | 1 |

| 1       | 1 | 0 | 0 | 0      | 1 | 0 |

| 1       | 1 | 1 | 0 | 0      | 1 | 1 |

| 1       | 1 | 1 | 1 | 1      | 0 | 0 |

| 0       | 1 | 1 | 1 | 1      | 0 | 1 |

| 0       | 0 | 1 | 1 | 1      | 1 | 0 |

| 0       | 0 | 0 | 1 | 1      | 1 | 1 |

| Table 1 |   |   |   |        |   |   |

| S | <i>Y</i> <sub>3</sub> <i>Y</i> <sub>2</sub> <i>Y</i> <sub>1</sub> <i>Y</i> <sub>0</sub> |

|---|-----------------------------------------------------------------------------------------|

| 0 | $J_{3}J_{2}J_{1}J_{0}$                                                                  |

| 1 | $K_3K_2K_1K_0$                                                                          |

Table 2

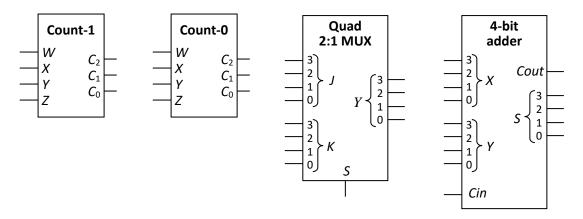

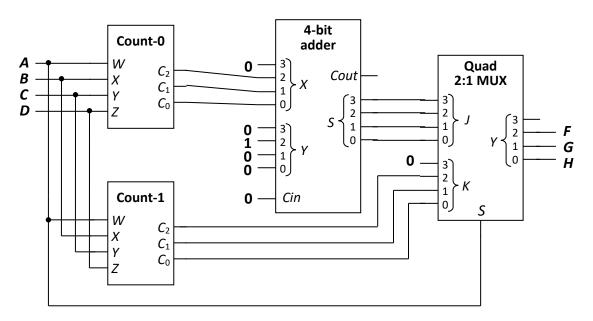

You are given the following components:

- a. A **Count-1** device that takes in a 4-bit input *WXYZ* and generates a 3-bit output  $C_2C_1C_0$  which is the number of 1s in the input. For example, if *WXYZ* = 0111, then  $C_2C_1C_0$  = 011 (or 3).

- b. A **Count-0** device that takes in a 4-bit input *WXYZ* and generates a 3-bit output  $C_2C_1C_0$  which is the number of 0s in the input. For example, if *WXYZ* = 0111, then  $C_2C_1C_0$  = 001 (or 1).

- c. A **quad 2:1 multiplexer** that takes in two 4-bit inputs  $J_3J_2J_1J_0$  and  $K_3K_2K_1K_0$ , and directs one of the inputs to its output  $Y_3Y_2Y_1Y_0$  depending on its control signal *S*, as shown in Table 2 above.

- d. A **4-bit parallel adder** that takes in two 4-bit unsigned binary numbers and outputs the sum.

The block diagrams of these components are shown below:

Given the above 4 components, you are to employ block-level design to design the converter, <u>without</u> <u>using any additional logic gate or other devices</u>. You may observe that if A = 1, then the output *FGH* is simply the number of 1s in the input *ABCD*. You are to make your own observation for the case when A = 0.

[Hint (not given in exam): You need only use one of each of the components. Complete the diagram below.]

| Key ideas:                                   |

|----------------------------------------------|

| 1. If A = 1 (or D = 0), count #1s in ABCD.   |

| 2. If <i>A</i> = 0 (or <i>D</i> = 1), either |

| a. <b>#1s + 2</b> × <b>#0s; or</b>           |

| b. 4 + #0s                                   |

OR

## 4. [AY2023/24 Semester 1 Exam]

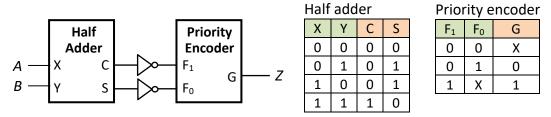

A Boolean function Z(A,B) is implemented using a half adder, two inverters, and a 2-to-1 priority encoder as shown below. The function tables of the half adder and priority encoder are also shown below.

The circuit above may be replaced by a single 2-input logic gate. What is the logic gate?

## Answer: NAND gate

| Х | Υ | С | S | $F_1$ | F <sub>0</sub> | G |

|---|---|---|---|-------|----------------|---|

| 0 | 0 | 0 | 0 | 1     | 1              | 1 |

| 0 | 1 | 0 | 1 | 1     | 0              | 1 |

| 1 | 0 | 0 | 1 | 1     | 0              | 1 |

| 1 | 1 | 1 | 0 | 0     | 1              | 0 |

## 5. [AY2023/24 Semester 1 Exam]

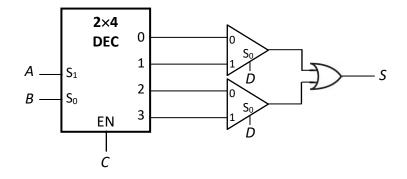

A Boolean function S(A,B,C,D) is implemented with a 2×4 decoder with one-enable, two 2:1 multiplexers and an OR gate as shown below.

## What is S(A,B,C,D) in $\Sigma m$ notation?

Answer:

$S(A,B,C,D) = \Sigma m(2,7,10,15).$

$S = (D' \cdot (C \cdot A' \cdot B') + D \cdot (C \cdot A' \cdot B)) + (D' \cdot (C \cdot A \cdot B') + D \cdot (C \cdot A \cdot B))$  $= A' \cdot B' \cdot C \cdot D' + A' \cdot B \cdot C \cdot D + A \cdot B' \cdot C \cdot D' + A \cdot B \cdot C \cdot D$

= m2 + m7 + m10 + m15