## RECONFIGURABLE HARDWARE SAT SOLVING

### WANG ZHANQING

(B.Eng. Beijing University of Aeronautics and Astronautics)

A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF SCIENCE DEPARTMENT OF COMPUTER SCIENCE SCHOOL OF COMPUTING NATIONAL UNIVERSITY OF SINGAPORE 2003 To My Parents

## Acknowledgements

First and foremost, I would like to thank my supervisors, Assoc. Prof. Roland Yap and Dr. Martin Henz, for their inspiration and continuous support of my Master of Science research, a great combination who are always willing to listen, encourage, and give insightful comments and valuable criticism. They read all the drafts of my thesis and taught me to be thorough in analyzing problems and rigorous in presenting ideas. This thesis would not have been possible without their support and guidance. I also thank my previous supervisor Prof. Joxan Jaffar who got me started in research.

My gratitude is also conveyed to all my previous and current colleagues in Programming Languages and Systems lab of NUS, for their cooperation and support during the time I studies here.

I am deeply grateful to my parents for their everlasting patience and love. I wish to thank my younger sister, my brother-in-law, my nephew, for just being there and providing me love and support. I also thank my husband for his encouragement and support. I wish to express my deepest appreciation to my lovely daughter for the happiness her smiling face and sweet words bring me.

Finally, to my new friend who kept me company and gave me support which have been my source of strength and the reason why I have come this far, I all of thank you!

## Contents

| List of Figures v |            |                                                               |          |  |  |  |

|-------------------|------------|---------------------------------------------------------------|----------|--|--|--|

| Li                | st of [    | Гables                                                        | viii     |  |  |  |

| Su                | mma        | ry                                                            | ix       |  |  |  |

| 1                 | Intr       | oduction                                                      | 1        |  |  |  |

| 2                 | Stoc       | hastic Local Search                                           | 4        |  |  |  |

|                   | 2.1        | Propositional Satisfiability (SAT)                            | 4        |  |  |  |

|                   | 2.2        | Stochastic Local Search (SLS)                                 | 5        |  |  |  |

|                   |            | 2.2.1 The GSAT Architecture                                   | 8        |  |  |  |

|                   |            | 2.2.2 The WalkSAT Architecture                                | 9        |  |  |  |

|                   |            | 2.2.3 WalkSAT Variants                                        | 11       |  |  |  |

|                   |            | 2.2.3.1 WalkSAT/TABU                                          | 11       |  |  |  |

|                   |            | 2.2.3.2 History Mechanism                                     | 11       |  |  |  |

|                   |            | 2.2.3.3 Self-Tuning Implementation of WalkSAT                 | 12       |  |  |  |

|                   |            | 2.2.3.4 Davis-Putnam Procedure + WalkSAT                      | 13       |  |  |  |

| 2                 | Dee        | anfiguus ble Computing Dave digu                              | 15       |  |  |  |

| 3                 |            | onfigurable Computing Paradigm                                | 15<br>15 |  |  |  |

|                   | 3.1<br>3.2 |                                                               |          |  |  |  |

|                   | 5.2        | Field Programmable Gate Array (FPGA).3.2.1Principle of FPGA.  | 17<br>20 |  |  |  |

|                   |            | 3.2.2 Structure of FPGA                                       | 20<br>22 |  |  |  |

|                   |            | 5.2.2 Structure of PT OA                                      |          |  |  |  |

| 4                 | Cu         | rrent SLS SAT Hardware Implementations                        | 25       |  |  |  |

|                   | 4.1        | One Flip per Clock Cycle for GSAT                             | 26       |  |  |  |

|                   | 4.2        | One Flip per Clock Cycle for WalkSAT                          | 29       |  |  |  |

|                   | 4.3        | GSAT Variant by Yung et al.                                   | 32       |  |  |  |

|                   | 4.4        | WalkSAT based on ROM Array                                    | 34       |  |  |  |

| 5                 | Cla        | use Evaluator without Re-Synthesis                            | 36       |  |  |  |

| 5                 | 5.1        | Compilation Time on Current Platform                          | 37       |  |  |  |

|                   | 5.2        | A General Clause Evaluator                                    | 41       |  |  |  |

|                   | 5.4        | 5.2.1 Decompose one Clause into Small Boolean Function Blocks | 41       |  |  |  |

|                   |            | 5.2.1 Execompose one clause into sman Boolean Function Blocks | 41       |  |  |  |

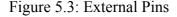

|                   |            | 5.2.1.2 Map Boolean Functions to RAM16x1Ds                    | 44       |  |  |  |

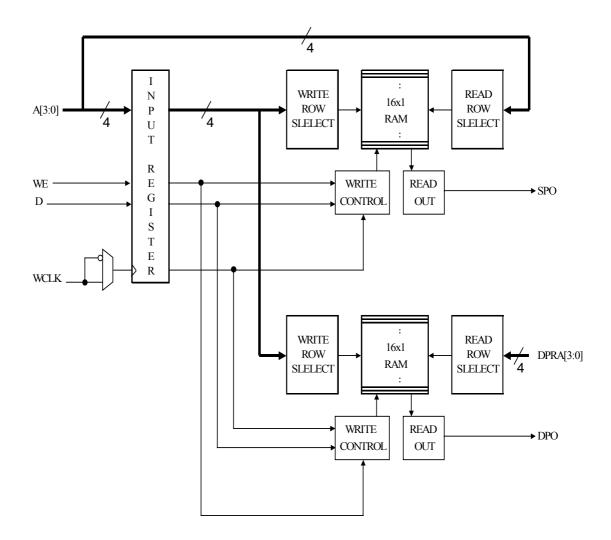

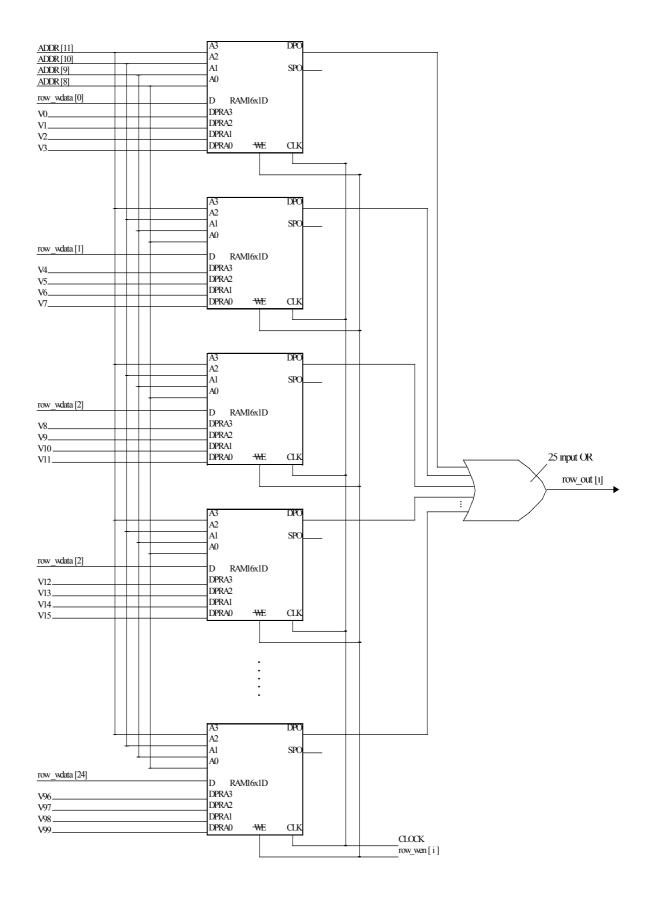

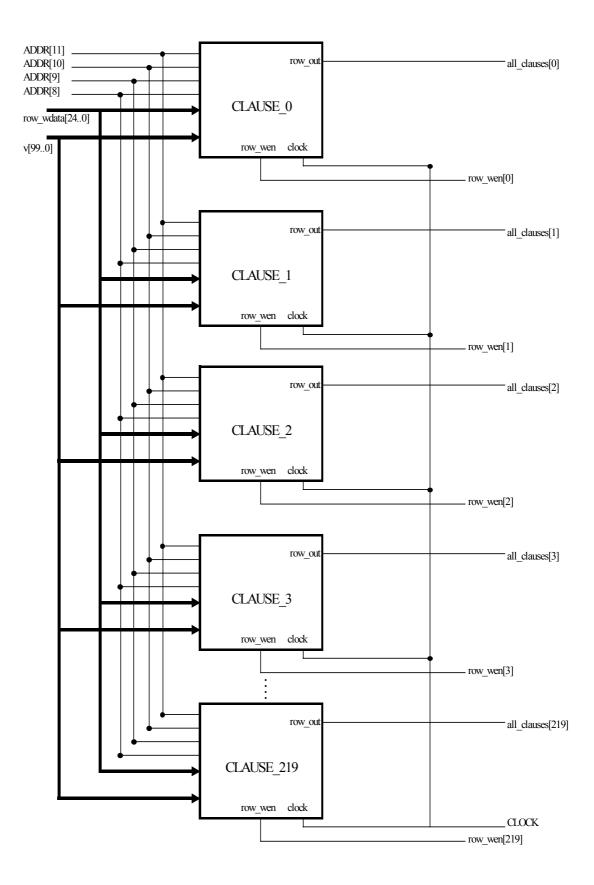

|                   |            | 5.2.2 Hierarchical Structure of our Clause Evaluator          | 45       |  |  |  |

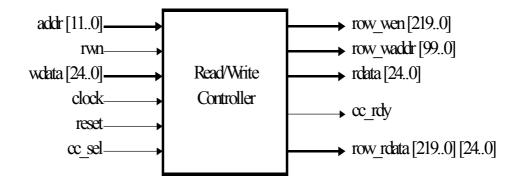

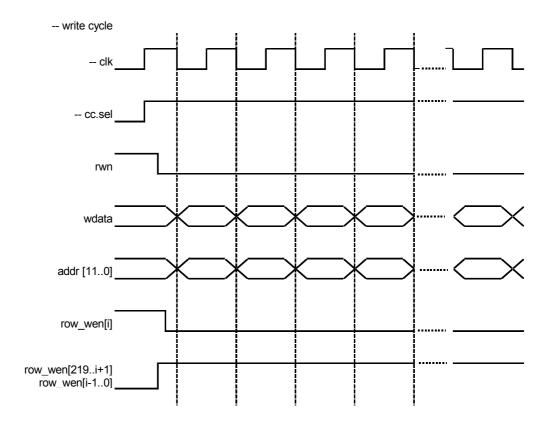

|    |        | 5.2.3 Control Logic inside our Clause Evaluator         | 51 |

|----|--------|---------------------------------------------------------|----|

| 6  | Imn    | olementation Platform                                   | 53 |

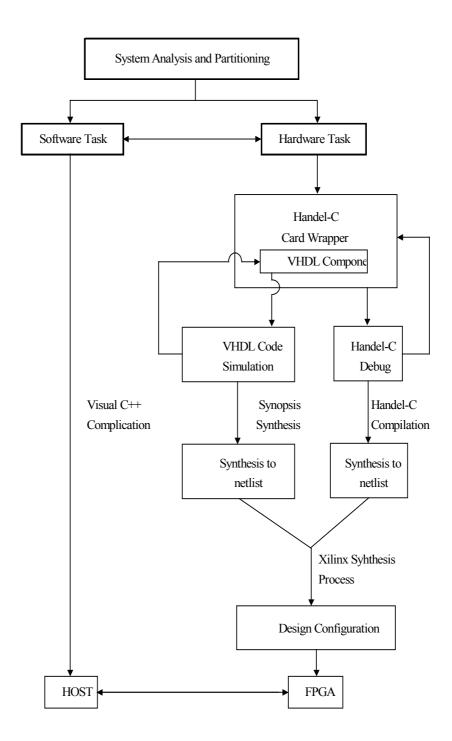

| Ū  | 6.1    | Handel-C vs. VHDL.                                      | 53 |

|    |        | 6.1.1 The Handel-C Programming Language                 | 53 |

|    |        | 6.1.2 VHDL Language Issues                              | 54 |

|    |        | 6.1.3 Discussion.                                       | 50 |

|    |        | 6.1.4 Combination of Handel-C and VHDL                  | 5′ |

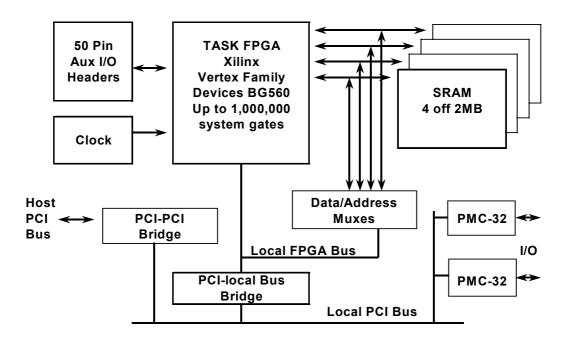

|    | 6.2    | RC1000-PP Prototyping Board                             | 60 |

| 7  | Two    | o Implementations of WalkSAT                            | 62 |

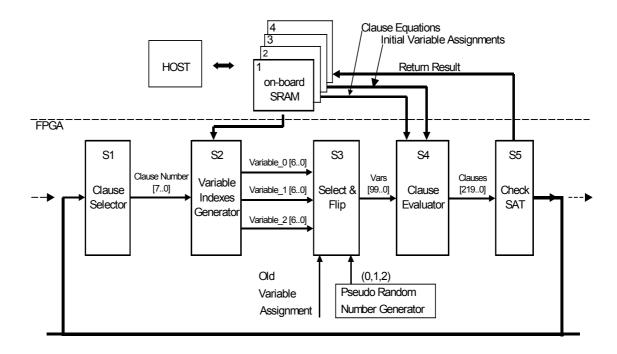

| ,  | 7.1    | Pipelined Random-strategy-based FPGA Implementation     | 6  |

|    | / • •  | 7.1.1 Five-stage Pipelined Random Implementation        | 64 |

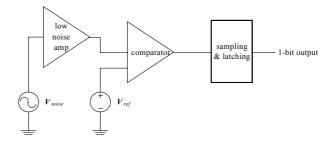

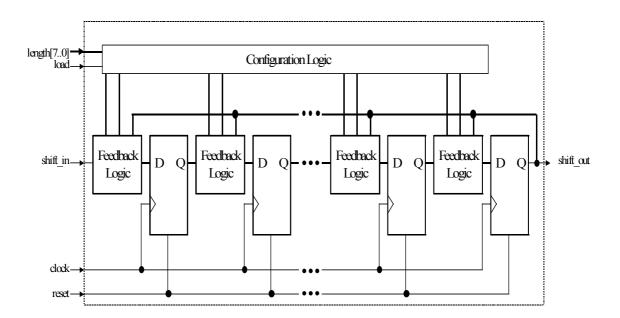

|    |        | 7.1.2 A Pseudo Random Number Generator                  | 60 |

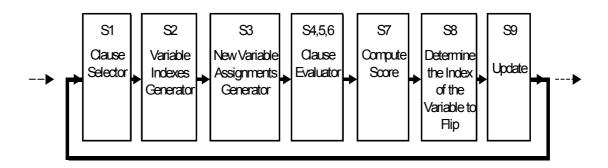

|    | 7.2    | FPGA Implementation of Greedy Selection                 | 69 |

| 0  | Б      |                                                         | -  |

| 8  | -      | erimental Results                                       | 70 |

|    | 8.1    | Benchmark Selection.                                    | 70 |

|    | 8.2    | Performance Comparison Scheme.                          | 72 |

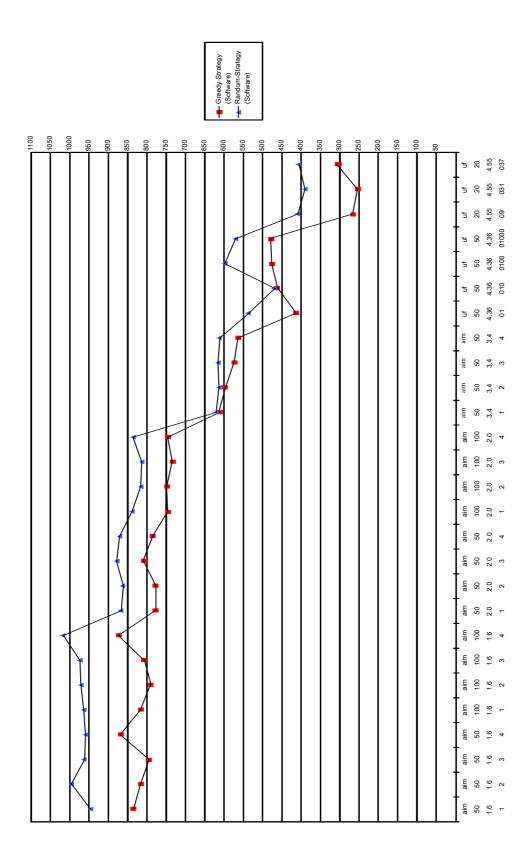

|    | 8.3    | Flip Rate Performance Comparison: Software vs. Hardware | 7  |

|    | 8.4    | Timing Performance.                                     | 78 |

|    | 8.5    | Time/Space Cost Comparison of FPGA-based Implementation | 82 |

| 9  | Con    | clusions                                                | 84 |

| A  | opend  | ix: Entity Declarations in VHDL                         | 80 |

|    | -      | ·                                                       |    |

| Bi | bliogr | <i>c</i> aphy                                           | 8  |

# **List of Figures**

| 2.1 | Stochastic Local Search Algorithm                                   | 6  |

|-----|---------------------------------------------------------------------|----|

| 2.2 | CHOOSE_FLIP Algorithm for GSAT                                      | 8  |

| 2.3 | Algorithm for WalkSAT-B Variant in WalkSAT Family                   | 10 |

| 3.1 | A Four- Input AND Gate Example                                      | 21 |

| 3.2 | Basic Structure of Xilinx SRAM-based FPGAs                          | 22 |

| 3.3 | Structure of Xilinx Virtex IOB                                      | 23 |

| 3.4 | Simplified Structure of Xilinx Virtex CLB                           | 24 |

| 4.1 | Basic CHOOSE_FLIP Design with Parallelized Variable Scoring         | 27 |

| 4.2 | Parallel CHOOSE_FLIP with Relative Scoring                          | 28 |

| 4.3 | A Four Stage Pipeline for GSAT                                      | 29 |

| 4.4 | Instance Specific Implementation of the WalkSAT Algorithm           | 31 |

| 5.1 | Space Cost & Compilation Time for GSAT Instance-Specific Designs    | 40 |

| 5.2 | Space Cost & Compilation Time for WalkSAT Instance-Specific Designs | 41 |

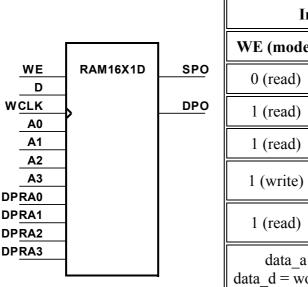

| 5.3 | External Pins                                                       | 42 |

| 5.4 | Function Block Diagram of RAM16x1D                                  | 43 |

| 5.5 | Hierarchy of a General Clause Evaluator                             | 48 |

| 5.6 | Structure of Clause <i>i</i>                                        | 49 |

| 5.7 | Structure of our General Clause Evaluator                           | 50 |

| 5.8 | External Connections of Read/Write Controller                       | 51 |

| 5.9 | Waveform of Write Cycle                                             | 51 |

| 6.1 | Design Flow of Handel-C and VHDL Combinatorial Method               | 59 |

| 6.2 | RC1000-PP Block Diagram                                       | 60 |

|-----|---------------------------------------------------------------|----|

| 7.1 | Random-strategy-based Implementation of the WalkSAT-B Variant | 65 |

| 7.2 | Pipelined Random-Strategy WalkSAT                             | 66 |

| 7.3 | A true 1-bit Random Number Generator                          | 67 |

| 7.4 | 8-bit LFSR PRNG Block Diagram                                 | 68 |

| 7.5 | Sequential Greedy-Strategy WalkSAT                            | 69 |

| 8.1 | Pure Software Flip Rate Performance Chart                     | 77 |

## **List of Tables**

| 2.1 | Example of a SAT Problem in <i>cnf</i>                          | 5  |

|-----|-----------------------------------------------------------------|----|

| 3.1 | Implementing a Four-Input AND Gate with the LUT in FPGA         | 21 |

| 5.1 | Time Spent on Re-synthesis for GSAT in Section 4.1              | 38 |

| 5.2 | Time Spent on Re-synthesis for WalkSAT in Section 4.2           | 39 |

| 5.3 | Mode Selection of RAM16x1D                                      | 42 |

| 5.4 | Decompose a Clause into Small Boolean Function Blocks           | 44 |

| 8.1 | The Benchmark Set                                               | 71 |

| 8.2 | Flip Rate Performance Comparison: Software versus FPGA-based    | 74 |

| 8.3 | Timing Performance Comparison based on Random Strategy          | 80 |

| 8.4 | Timing Performance Comparison based on Greedy Strategy          | 81 |

| 8.5 | Running Time Comparison between Random-Strategy Implementations | 82 |

| 8.6 | Time/Space Cost Comparison of FPGA-based Implementation         | 83 |

## **Summary**

Boolean satisfiability (SAT) problems are NP-complete problems that are well-known in areas of operations research, artificial intelligence and computer-aided design. Algorithms for solving NP-complete problems may have long running times. To improve the performance of SAT solvers, hardware processing elements are used to accelerate execution. There has been considerable recent interest in the application of Field Programmable Gate Arrays (FPGAs) devices as accelerators for solving SAT problems.

There are two main types of SAT solvers, complete solvers, e.g. Davis-Putnam (DP), and incomplete Stochastic Local Search (SLS) methdos. The DP procedure is a complete branch and bound algorithm that is able to prove both satisfiability and unsatisfiability; whereas the SLS procedure is an incomplete algorithm and may not find a solution even if one exists. SLS algorithms have been successful for solving SAT problems. The WalkSAT family of algorithms contains some of the best performing SLS algorithms and has a very simple structure, thus can be improved by extracting more parallelism. There are a number of such hardware designs and implementations using reconfigurable FPGAs in the existing literature.

The use of hardware SAT solver only makes sense if there is significant performance advantage compared to software. Software can make use of state of the art processors built with the latest processor technology. A hardware SAT solver, on the other hand, is less likely to have the same level of process technology, and hence longer cycle times. Earlier hardware implementations did not outperform optimized software. One new instance-specific approach was to maximize performance by making full use of parallelism and enabled a performance of one flip per clock cycle, more than two orders of magnitude faster than software. However, an important limitation of all these previous work is that they generated a high level description of a circuit customized for a particular SAT problem. Since the time needed to re-synthesis, map, place and route the new design is likely to significantly exceed the runtime improvement from faster software SAT solver, the approach of custom design specific to a particular SAT problem instance is not practical.

This thesis explores FPGA-based hardware designs for WalkSAT, which are not instance-specific and thus not require re-synthesis. In addition to this requirement, a hardware implementation faces interesting design tradeoffs due to the inherently limited logic resources on the chip. We propose two versions of WalkSAT, which allow real-time reconfiguration. The differences of the two WalkSAT versions lead to different design choices for maximal performance. The first design emphasizes fast cycle times (one flip per clock cycle), employing random variable selection to allow for a pipelined design. The second uses a greedy variable selection heuristic, which precludes pipelining, exemplifying a tradeoff between flip rate and effectiveness of variable selection. Both design have improved performance over other published nonre-synthesis SLS FPGA implementations.

## **Chapter 1**

### Introduction

Recent improvements of Field Programmable Gate Array (FPGA) technology have made FPGA's a viable platform for development of hardware accelerators, while still allowing design flexibility and promise of design migration to future technologies. Many members of the computing community are eyeing FPGA-based platforms as a way to provide rapidly deployable, flexible, and portable hardware solutions.

Using FPGA components in the content of propositional satisfiability problem (SAT) solving introduces challenges in system architecture and logic design. Stochastic local search (SLS) algorithms have been a successful approach for solving SAT problems. The WalkSAT family of algorithms [SKC94, MSK97] contains some of the best performing SLS algorithms. SLS algorithms like WalkSAT have a very simple structure and are composed of essentially three steps which are iterated until a satisfiable solution is found: (i) evaluate clauses; (ii) choose a variable; and (iii) flip the variable's Boolean value.

Since each of the steps is simple, moreover SAT clauses can be directly represented in hardware, it is tempting to build a hardware SLS solver. There are a number of such hardware designs and implementations [HM97, YSLL99, LSW01,

HTY01] using reconfigurable FPGA hardware. Hardware approaches to systematic search procedures for SAT problems are beyond the scope of this thesis; see [AS00] for an overview.

The use of hardware SAT solvers only makes sense if there is significant performance advantage compared to software. Software can make use of state of the art processors built with the latest processor technology. A hardware SAT solver, on the other hand, is less likely to have the same level of process technology, and hence longer cycle times. Earlier hardware implementations like [HM97, YSLL99] did not outperform optimized software. For example, a reimplementation of the design in [HM97] which was done in [HTY01] had flip rates between 98 – 962 Kflips/s. In some problems, this was a bit faster than software and in other cases slower. In [HTY01], it was shown that GSAT SLS solvers running at one flip per clock cycle was achievable with performance gains of about two orders of magnitude over software. That implementation makes use of the reconfigurable nature of FPGAs to build a custom design specific to a particular SAT problem instance. While [HTY01] shows that very large speedups are feasible, this approach is not practical as a general SAT problem solver, because the time to re-synthesize, place and route the new design for an FPGA is likely to significantly exceed the runtime improvement from the faster solver.

In the brief survey above of relevant work, we have observed that while some of these efforts have focused on the design of instance-specific solving system, there has been less work in the area of implementing a practical design in a real time environment. Typically an instance-specific hardware accelerator is not practical, because the re-synthesis requirements are often time consuming, it is necessary to find a solution. To help address this challenge we have created the design without re-synthesis. In this thesis, we explores hardware designs for WalkSAT, which are not instancespecific and thus do not require re-synthesis. In addition to this requirement, a hardware implementation faces interesting design tradeoffs due to the inherently limited logic resources on the chip. We propose two versions of WalkSAT, which allow real-time reconfiguration. The differences of the WalkSAT versions lead to different design choices for maximal performance. The first design emphasizes fast cycle times (one flip per clock cycle), employing random variable selection to allow for a pipelined design. The second uses a greedy variable selection heuristic, which precludes pipelining, exemplifying a tradeoff between flip rate and effectiveness of variable selection. Both designs have improved performance over published SLS FPGA implementations without re-synthesis.

The remainder of this thesis is structured as follows: Chapter 2 introduces the background related to stochastic local search. Chapter 3 gives an overview on FPGA technology and its usage in reconfigurable computing and design prototyping. Chapter 4 discusses some of the current reconfigurable implementations of SAT solvers. From their design limitations, we presented a clause evaluator without re-synthesis in Chapter 5. Chapter 6 addresses our implementation platform. Chapter 7 describes our two WalkSAT implementations based on two strategies. Chapter 8 reports the experimental results. Finally, Chapter 9 concludes and offers suggestions for future work.

### Chapter 2

## **Stochastic Local Search**

Local search algorithms are among the standard methods for solving propositional satisfiability problems from various areas of computer science. After its introduction by Selman, Levesque, and Mitchell [SLM92] and Gu [Gu92], a large number of such algorithms were proposed and investigated. In this thesis, we focus on WalkSAT family of stochastic local search. WalkSAT algorithms are in general sound. In this thesis we will discuss variants of WalkSAT family.

### **2.1 Propositional Satisfiability (SAT)**

In 1971, propositional satisfiability (SAT) was introduced as the first computational task to be NP-complete [Coo71]. As SAT is the conceptually simplest NP-complete problem, a wide range of other problems can be encoded into SAT; which make SAT a useful problem.

SAT problems can be presented as a set of propositional clauses in conjunctive normal form (*cnf*). In this form, the problem is basically a conjunction of clauses, wherein each clause is a disjunction of literals. A literal is then a propositional variable or its negation. An example of a *cnf* problem is shown in Table 2.1. A solution to a

SAT problem is a variable assignment that satisfies all the clauses according to a rule of interpretation. For the example *cnf* problem below, one possible solution has an assignment of vI = 1, v2 = 0, v3 = 1, v4 = 0. The *cnf* is a popular standard format for encoding SAT problems.

| variables | <i>v1, v2, v3, v4</i>                                     |         |                                |  |

|-----------|-----------------------------------------------------------|---------|--------------------------------|--|

| literals  | v1, ¬v1                                                   | 4, ¬v4  |                                |  |

| cnf       | $clause1 \land clause2 \land clause3 \land \land clause8$ |         |                                |  |

| clause1   | $v1 \lor v2 \lor v3$                                      | clause5 | $v1 \lor v3 \lor v4$           |  |

| clause2   | $vl \lor v2 \lor v4$                                      | clause6 | $\neg v2 \lor v3 \lor \neg v4$ |  |

| clause3   | $\neg v1 \lor \neg v2 \lor \neg v3$                       | clause7 | $v1 \lor \neg v3 \lor \neg v4$ |  |

| clause4   | $\neg v1 \lor \neg v2 \lor v3$                            | clause8 | $v2 \lor v3 \lor v4$           |  |

Table 2.1: Example of a SAT Problem in *cnf*

### 2.2 Stochastic Local Search (SLS)

Stochastic local search is best viewed as a model-finding procedure wherein finding a solution to a problem determines its satisfiability. This is different from other theoremproving procedures that look for a sound and formal proof of the satisfiability. In order to understand this model-finding procedure, we define *variable space* to be the set of all the possible combinations on truth value assignments for each variable in a given SAT problem. A procedure like Davis-Putnam [DP60] or ASAT [DABC93] performs deterministic search over the whole problem. These are called as complete procedures which can determine either the satisfiability or unsatisfiability of the SAT problem. SLS algorithms on the other hand are incomplete procedures with the advantage of having a more efficient search traversal that could solve the problem with less time. An incomplete procedure might be capable of prove satisfiability by finding a solution but will never establish unsatisfiability. Their main idea is to perform an indeterministic non-backtracking local search over the *variable space* to find a solution that satisfies the *cnf*. This local search strategy has shown to be robust and could outperform other systematic SAT solvers as presented in [SLM92], [Gu92], and [HS99].

The local search starts with an initial variable assignment or initial state. If the current state does not satisfy the *cnf*, the search strategy is to move to an adjacent state that has a difference of one or more variables depending on its preset Hamming distance. For a Hamming distance of one, the neighboring states would be the states that only have one different variable assignment. The search strategy will do repeated moves until a satisfiable assignment is found or the time-out limit on moves is reached. The limit imposed for this type of algorithms should be high enough that satisfiable problems are detected with high accuracy. For the WalkSAT and GSAT algorithms investigated in this thesis, the Hamming Distance is set to one.

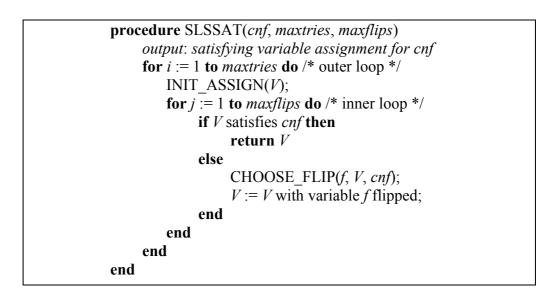

Figure 2.1: Stochastic Local Search Algorithm

A general outline for the Stochastic Local Search algorithm **SLSSAT** is given in Figure 2.1. **SLSSAT** algorithms are different in two aspects, namely: the generation of the initial assignment (**INIT ASSIGN**) and the selection for the next state (CHOOSE\_FLIP). All the investigated SLSSAT algorithms have a common INIT\_ASSIGN procedure that randomly chooses the initial assignment from the variable space according to a uniform distribution. Hence, we concentrate on the CHOOSE\_FLIP procedure that differentiate the investigated SLSSAT algorithms. As shown in Figure 2.1, there are two limits imposed in the algorithms. As the algorithm repeatedly performs flips to the current state, we limit the number of repetitions to *maxflips*. When it reaches *maxflips* with no solution found, the algorithm would exit the inner loop and restart with a new initial assignment. This stage is essential for the algorithm to escape from the local minima in the variable space. It means that for SLSSAT algorithms there exists a state in the *variable space* from which a solution will not be reached without reinitializing the search. The second time-out stage ends the execution of the algorithm when a certain number of tries (*maxtries*) has been reached. In that case, the algorithm fails to prove satisfiability.

For the **CHOOSE\_FLIP** procedure, the *score*, which is the number of clauses satisfied by variable assignment *V*, plays a crucial role in the selection for the next variable to flip. We declare some *score* and additional functions that will be used in the following sections.

- 1. The function *score(cnf, V)* returns the number of clauses satisfied as a results of using a variable assignment *V* in *cnf*.

- 2. The function *score<sub>f</sub>(i, cnf, V)* returns the number of clauses in *cnf* that are satisfied by using the modification of the assignment V where the truth value of the *i*-th variable is inverted.

- 3. The function  $score_b(i, cnf, V)$  returns the number of clauses in cnf that would be broken (unsatisfied) when the truth value for the *i*-th variable in V is flipped.

- 4. The function **CHOOSE\_ONE** returns an element from a sequence using uniform distribution.

- 5. The function **UNSATISFIED** returns a sequence of unsatisfied clauses from *cnf* for the variable assignment of *V*.

### 2.2.1 The GSAT Architecture

The greedy local search procedure called GSAT was first introduced by Selman, Levesque, and Mitchell [SLM92] and Gu [Gu92] in 1992. Since then, a number of GSAT variants have been derived such as GSAT with Tabu Search (GSAT/TABU) [MSK97, MSG97, SSS97] and GSAT with History (HSAT) [GW93]. Figure 2.2 shows the **CHOOSE\_FLIP** procedure used by GSAT. The procedure **CHOOSE\_FLIP** gathers the variables that produce the highest *scoref* in the sequence named *scores* and performs a random selection in function **CHOOSE\_MAX** to determine the next variable *f* to flip. This algorithm is referred to as 'greedy' since it assumes that a neighboring *state* with the highest *scoref* would have the highest probability leading to a solution.

| <pre>procedure CHOOSE_FLIP(f, V, cnf)</pre> |                                                                     |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------|--|--|--|

|                                             | output: variable f that produces the maximum score                  |  |  |  |

|                                             | <b>for</b> $i := 1$ <b>to</b> $n$ <b>do</b> /* for all variables */ |  |  |  |

| $scores[i] := score_f(i, cnf, V);$          |                                                                     |  |  |  |

|                                             | end                                                                 |  |  |  |

|                                             | return CHOOSE_MAX(scores);                                          |  |  |  |

| end                                         |                                                                     |  |  |  |

Figure 2.2: CHOOSE\_FLIP Algorithm for GSAT

A straightforward implementation of GSAT in Figure 2.2 from [SLM92] is rather inefficient, since for each call to CHOOSE\_FLIP the scores for all the variables are recalculated. An implementation of GSAT by Selman and Kautz version 41 (GSAT41)

is an optimized software implementation that usually serves as a reference benchmark implementation. Their method to efficiently implement GSAT is to evaluate the affected *scores* of some variable after each variable flip. A detailed description of GSAT41 together with a complexity analysis is given in [Hoo96].

#### 2.2.2 The WalkSAT Architecture

The WalkSAT architecture is based on ideas first published by Selman, Kautz, and Cohen in 1994 [SKC94] and it was later formally defined as an algorithmic framework by McAllester, Selman, and Kautz in 1997 [MSK97]. WalkSAT is a family of stochastic algorithms that assigns all the variables a random truth assignment and then attempts to heuristically refine the assignment until all the clauses evaluate to true. WalkSAT is based on a 2-stage variable selection process focused on the variables occurring in currently unsatisfied clauses. For each local search step, in a first stage a currently unsatisfied clause c' is randomly selected. In a second step, one of the variables appearing in c' is then flipped to obtain the new assignment. Thus, while the GSAT architecture is characterized by a static neighborhood relation between assignments with Hamming distance one, WalkSAT algorithms are effectively based on a dynamically determined subset of the GSAT neighborhood relation.

WalkSAT family is in general a kind of robust stochastic local search algorithm. In WalkSAT family, the specific method of varying the truth assignment defines the variant of WalkSAT. All variants share the common behavior of occasionally ignoring their heuristic and making a random refinement according to some fixed probability.

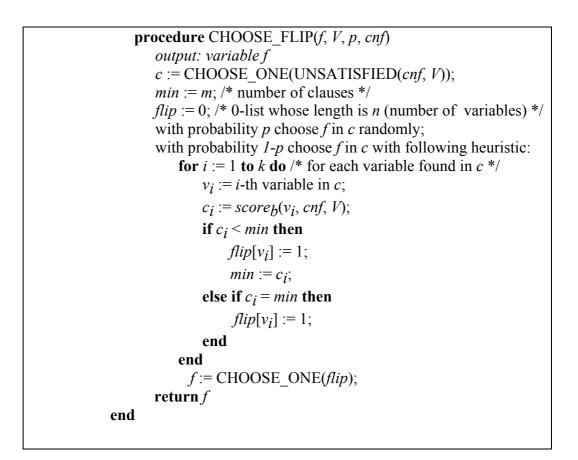

In our FPGA-based WalkSAT implementations described in Chapter 7, the algorithm we adapted is based on a variant called WalkSAT-B [MSK97]. Figure 2.3 briefly describes this algorithm.

In Figure 2.3, given a SAT problem instance in format *cnf*, a random truth assignment V, and a noise setting p, the procedure will return a variable f which will be the next to be flipped. The function **UNSATISFIED** returns a list of clauses that are unsatisfied by the assignment of V. Then randomly choose an unsatisfied clause c in this list. Following, with probability p choose f in c randomly; with probability 1-p choose f with the smallest *scoreb*.

Figure 2.3: Algorithm for WalkSAT-B Variant in WalkSAT Family

As discussed in [MSK97], it is well known that the performance of a stochastic local search procedure depends upon the setting of its noise parameter, and that the optimal setting varies with the problem distribution. It is therefore desirable to develop general principles for tuning the procedures. In [MSK97], they presented two statistical

measures of the local search process that allow one to quickly find the optimal noise settings. These properties are independent of the fine details of the local search strategies, and appear to be relatively independent of the structure of the problem domains.

In Chapter 7, we investigate two extreme implementations based on the above WalkSAT variants by setting p to 1 (Random-Strategy) and 0 (Greedy-Strategy) respectively.

### 2.2.3 WalkSAT Variants

#### 2.2.3.1 WalkSAT/TABU

A well-known search mechanism in WalkSAT family is called WalkSAT/TABU which uses Tabu Search [MSK97]. It uses the same two-stage selection mechanism and the same scoring function *scoreb* as WalkSAT and additionally enforces a *tabu* tenure. A local search can be stuck at a local minima when it actually performs variable flips over a certain variable pattern. In order to avoid the repeating patterns, all recently flipped variables are restricted from getting flipped again for a certain duration. This duration is usually based on the number of variable flips, which is often referred to as *tabu* tenure. With the addition of the *tabu* mechanism the local search will hopefully be forced to flip a different variable that breaks the pattern and escapes the local minima. This however is not a guaranteed performance and is only a heuristic. As for the length of the *tabu* tenure, there is still no formal function for it to attain the Probabilistic Approximate Completeness (PAC) property.

#### 2.2.3.2 History Mechanism

The history mechanism, as the name implies, makes use of history information in guiding the local search of SLSSAT. Typically, in the situation where several variables with the same *score* arise, a random selection over uniform distribution is done. In this procedure, it would be possible to have variables that are never chosen even though they have been eligible many times. The history information eliminates this scenario by adding an additional step in the variable selection process whenever tie-breaking between variables is needed. This step would select the variables that are the least recently flipped. Although this may appear to be an unimportant addition to the algorithm, results from [GW93] show that SLSSAT combined with history provides superior performance.

#### 2.2.3.3 Self-Tuning Implementation of WalkSAT

The ability of stochastic satisfiability solvers to successfully find a problem's solution depends on how the trade-off between random decisions and heuristic decisions is managed during the solution search. This trade-off is controlled by a parameter setting, typically called the noise, which ranges from 0% to 100%. The optimal noise setting can vary greatly depending on the specifics of the algorithm used and the problem being solved. For a particularly hard problem, whose solution is unknown, it would be very useful to know the optimal noise setting.

In [PK01], Donald J. Patterson and Henry Kautz presented an algorithm that uses a variant of WalkSAT [SCK94] to probe the parameter space of noise settings for the value which will maximize the probability of finding a solution. In [PK01], they introduce *Auto-WalkSAT* which is a general algorithm that automatically tunes any variant of the WalkSat family of stochastic satisfiability solvers.

In [PK01], their algorithm *Auto-WalkSAT* is able to successfully minimize the invariant ratio using a bracketed search supplemented with parabolic interpolation. The additional overhead of minimizing this ratio is very small, adding approximately one minute to the running time of the algorithm. Using a heuristic of adding ten percent noise to this value, *Auto-WalkSat* then efficiently solves many problems which critically depend on a proper noise setting.

#### 2.2.3.4 Davis-Putnam Procedure + WalkSAT

WalkSAT is an incomplete method and is claimed to be more efficient than Davis-Putnam Procedure [DLL62] which is a complete method. However, WalkSAT may come into difficulties on big SAT instances with many variables. In [ZHZ02], Wenhui Zhang *et al.* improved the efficiency by combining the Davis-Putnam procedure and the WalkSAT algorithm.

In 1960, Davis Putnam introduced a resolution algorithm for solving propositional satisfiability, which is called as the Davis-Putnam algorithm [DP60]. After two years, Davis, Logemann and Loveland improved on the algorithm and developed the Davis-Putnam procedure [DLL62]. The former algorithm uses an elimination rule, while the latter which became more famous uses backtracking. Further references to both works became ambiguous, but are likely to refer to the Davis-Putnam Procedure. The detailed algorithm for Davis-Putnam procedure can be found in [DLL62] which is the backtracking search algorithm.

Davis-Putnam procedure is one of the most efficient complete search algorithm for SAT. Many systems based on this procedure have been implemented and many interesting problems have been solved by these tools. A major problem with DP is that it may have to go through a very large search space.

In [ZHZ02], a hybrid approach was adopted. Firstly, use the DP procedure partially, and produce some subproblems. Then the subproblems are given to WalkSAT. In [ZHZ02], there are two parameters for controlling the number of subproblems. One is the maximum depth to be searched by DP, the other is the maximum number of subproblems.

If a subproblem is proven to be satisfiable within the given depth, the satisfiability checking is also finished. Otherwise, the subproblems which have not yet been proven to be unsatisfiable are recorded in files. In each subproblem, the propositional variables are renumbered consecutively from 1 to the number of remaining variables. These subproblems are given to WalkSAT in a loop until a solution is found or the maximum number of repetitions is reached.

The advantage of partitioning a problem into subproblems compared to using WalkSAT alone is that each subproblem is much smaller than the original problem. The implication of this is that the time needed for each trial of such a subproblem with WalkSAT is much shorter; and a solution of such a subproblem is expected to be found with much less time, if this subproblem indeed has a solution. For hard SAT instances, the speed up with their approaches is significant.

### Chapter 3

## **Reconfigurable Computing Paradigm**

Reconfigurable computing is a new and emerging computing paradigm that uses reconfigurable hardware, like Field Programmable Gate Arrays (FPGAs), to implement computationally intensive tasks. An FPGA provides the benefits of a customized CMOS-VLSI chip, and at the same time, avoids the fabrication cost and inherent risk of using conventional masked gate array. Similar to current applicationspecific hardware accelerators, reconfigurable hardware benefits from the customization of data widths, instructions, memory access, etc. as compared to general-purpose computer. The resulting hardware can be optimally designed for the target application and exploits fine-grain parallelism.

### 3.1 General-Purpose Computer vs. Special-

### **Purpose Computer**

When we use the word "computer", we are normally referring to a general-purpose computer. By definition, general-purpose computers are computing machines that can

be used for a wide range of applications. On the other hand, there are also special purpose computers used for a single application or a class of similar applications.

The design of a general-purpose computer takes into account a wide range of considerations and constraints. Through several generations, a family of general-purpose computers often maintains a relatively stable instruction set. There are many applications available for these computers. In addition, programming for such computers is very easy because there are many software tools available. General-purpose computers offer good performance on wide range of applications at a very reasonable price.

For a particular application, however, a general-purpose computer does not always provide the highest performance. When the performance requirement of certain applications exceeds the performance of the available general-purpose computer, there are different approaches to create higher performance computing machines to provide the necessary computing power. One way is through parallel computing. A number of general-purpose processors can be combined to form a parallel computer. Very high performance can be achieved by partitioning the problem into small pieces and letting many computers work in parallel to solve the problem. However, the application should be suitable for such parallel computing. Another approach is to build specialized computers according to the application to provide higher performance specially for this application. The application-specific approach may provide very high performance for the targeted application, often with less hardware usage than the parallel computing approach.

There is one major obstacle in building application-specific computing machines. That is the cost for designing and building such a computer. The initial cost for designing and manufacturing integrated circuit (ICs) is very high and the subsequent cost for fabricating the IC is relatively small. When an integrated circuit is fabricated in large quantities, the initial cost can be amortized and each chip produced is only responsible for a small portion of the initial cost. This is the major reason that popular general-purpose computers can be sold at relatively low prices. On the other hand, special-purpose computers require special-purpose integrated circuits. The initial cost is so high that it may dominate the total cost of building such system. It lacks the economy of scale.

Another difficulty with the special-purpose approach is the development time. It often takes a very long time to develop such a system, because a large amount of work is involved. Because the performance of general-purpose computer improves very quickly, special-purpose hardware may become obsolete very soon.

Taking into the cost and short life, special-purpose computers are not an attractive approach unless the need for such hardware is very strong. However, if the cost and development time can be significantly reduced, this can be a viable approach for many problems.

### 3.2 Field Programmable Gate Array (FPGA)

Reconfigurable computing is a novel approach that combines the strengths of general purpose computing and the special-purpose approach. The research for reconfigurable computing is motivated by pursuit of higher computing performance with modest hardware cost. The advances in integrated circuits has brought about the class of programmable logic devices that can achieve high computing performance and yet provide the flexibility of gate-level programmable Gate Array (FPGA) [BFRV92, Sha99]. The basic idea of reconfigurable computing is to build a hardware system

based on FPGAs or other programmable devices. This system is configured, or programmed, according to a particular application to achieve high performance. On the other hand, the hardware should be general enough that many different applications can be mapped to the same hardware and run quickly.

The advent of reconfigurable computing bridges the gap between general-purpose processors and special-purpose computers or accelerators. It blurs the distinction between hardware and software. The study of reconfigurable computing also brings together knowledge on computer architecture, parallel computing, compilers, software development, hardware and IC design, and VLSI CAD.

A general-purpose computer has a fixed instruction set. Different applications are implemented using different software programs. User programming is performed at the instruction level. Reconfigurable computing takes a different approach. There is no fixed instruction set. Instead of a general-purpose processor, reconfigurable computing uses FPGAs as the computing elements. The FPGAs are essentially integrated circuits that can be configured into specific logic functions. Different applications are realized by different configurations for hardware. The user programming can be performed at the logic gate level. Reconfigurable computing achieves high performance by creating specific functional units and better exploiting the parallelism.

A reconfigurable hardware system normally cannot operate as a stand-alone machine. It should work in tandem with a general-purpose processor, called a host machine. The host machine should handle the operating system and many basic functions such as program loading, file I/O and control functions. There can be different coupling mechanisms between the reconfigurable computer and the host. There have been proposals and recent design work on very closely coupled architectures, in which the processor and the FPGA are located on the same chip

[RS94, RLG98]. There are less closely coupled systems, in which the FPGA communicates with the processor through some I/O bus [GHK91, VBR96]. This has an impact on the communication bandwidth and latency, hence how the application is implemented. It will affect the programming model and performance model of the implementation.

Secondly, there are differences in total logic capacity of reconfigurable systems. The number of FPGA chips ranges from one to a few dozens or even thousands. The logic capacity determines the maximum complexity of application that can be mapped to hardware. It places an upper limit of parallelism that can be exploited.

There are also differences in the programming model of reconfigurable hardware. In some systems, all instructions are compiled into an FPGA hardware configuration. In other systems the reconfigurable hardware supports a limited instruction set. In this case, the programming model bares some similarity with general-purpose processor with the added flexibility in the instruction set. An application can be either fully implemented on reconfigurable hardware or partitioned between reconfigurable hardware and a general-purpose computer.

An FPGA is a type of programmable device, wherein a general-purpose chip can be configured to perform a wide variety of applications. The first programmable device that has achieved widespread use was the PROM (Programmable Read-Only Memory). PROMs, a one-time programmable device come in two basic versions: the Mask-Programmable Chip programmed only by manufacturer, and the Field-Programmable Chip programmed by the end-user. The Field Programmable PROM developed into two types, the Erasable Programmable Read-Only Memory (EPROM) and the Electrically Erasable Programmable Read-Only Memory (E<sup>2</sup>PROM). The  $E^2$ PROM has the advantage of being erasable and re-programmable many times. Another step took place in this field which lead to the development of the Programmable Logic Device (PLD). These devices were constructed to implement logic circuits. The PLD include an array of AND-gates connected to an array of OR-gates. The PAL (Programmable Array Logic) is a commonly used PLD consisting of a programmable AND-plane followed by a fixed OR-plane. PALs come in both mask and field versions. The PAL was designed for small logic circuits.

The Mask-Programmable Gate Array (MPGA) was developed to handle larger logic circuits. A common MPGA consists of rows of transistors that can be interconnected to implement desired logic circuits. User specified connects are available both within the rows and between the rows. This enables implementation of basic logic gates and the ability to interconnect the gates. As the metal layers are defined at the manufacturer, significant time and cost are incurred in producing the run. In 1985, Xilinx Inc. introduced the FPGA (Field Programmable gate Array). An FPGA is a universal logic device structures as an array of user programmable logic and I/O cells interconnected by a programmable routing network.

There are four FPGA technologies in use: static Ram cells, anti-fuse, EPROM transistors, and E<sup>2</sup>PROM transistors. For this discussion, we focus on the static RAM technology on symmetrical array configuration developed by Xilinx. In the static RAM FPGA, programmable connections are made using pass-transistors, transmission gates, or multiplexers that are controlled by SRAM cells. Only SRAM cells allow fast in-circuit reconfiguration for any number of times. The major disadvantage, on the other hand, is the size requirement of the RAM technology.

### 3.2.1 Principle of FPGA

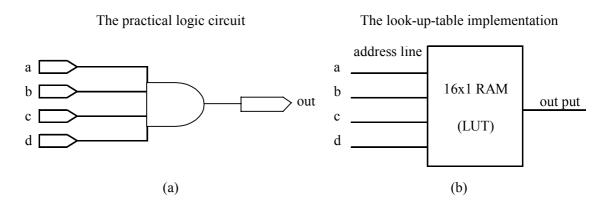

FPGAs are based on the structure of Look-Up-Table (LUT), and LUT is essentially a RAM. Currently, most FPGAs adopt 4-input LUT, thus each LUT can be viewed as a 16-deep and 1-bit RAM with a 4-input address line. From a schematic or VHDL code, the synthesis tool computes all possible results and writes these results into the RAM.

Figure 3.1: A Four- Input AND Gate Example

Figure 3.1 shows a 4-input AND gate example. Sub-figure (a) describes the schematic of the practical logic circuit of a 4-input AND gate; sub-figure (b) is the Look-Up-Table implementation respondent to sub-figure (a).

| 4-input A       | ND Gate      | 16-deep and         | 1-bit RAM       |

|-----------------|--------------|---------------------|-----------------|

| input of "abcd" | logic output | address line "abcd" | data in 16x1RAM |

| 0000            | 0            | 0000                | 0               |

| 0001            | 0            | 0001                | 0               |

| 0010            | 0            | 0010                | 0               |

| 0011            | 0            | 0011                | 0               |

| 0100            | 0            | 0100                | 0               |

| 0101            | 0            | 0101                | 0               |

| 0110            | 0            | 0110                | 0               |

| 0111            | 0            | 0111                | 0               |

| 1000            | 0            | 1000                | 0               |

| 1001            | 0            | 1001                | 0               |

| 1010            | 0            | 1010                | 0               |

| 1011            | 0            | 1011                | 0               |

| 1100            | 0            | 1100                | 0               |

| 1101            | 0            | 1101                | 0               |

| 1110            | 0            | 1110                | 0               |

| 1111            | 1            | 1111                | 1               |

Table 3.1: Implementing a Four-Input AND Gate with the LUT in FPGA

In Table 3.1, column 1 shows the input signals "abcd" of the four-input AND gate, column 2 shows the expected output of the four-input AND gate when input signals are as in column 1. Column 3 shows signals on the 4-bit address line of the 16x1 RAM, column 4 shows the data stored in this 16x1 RAM and addressed by "abcd" shown in column 3. Thus, a four-input AND gate can be implemented with the Look-Up-Table structure in FPGA.

#### 3.2.2 Structure of FPGA

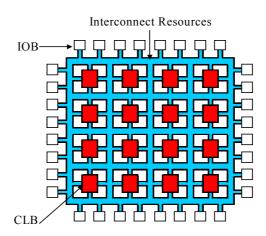

An FPGA is an integrated circuit (IC) that can be programmed after manufacture. Since it is re-programmable on the field, it is a kind of reconfigurable hardware. Typical architecture of an FPGA comprises a regular array of *Configurable Logic Blocks* (CLBs) with routing resources for interconnection and surrounded by programmable *Input/Output Blocks* (IOBs). CLBs provide the functional elements for constructing logic while IOBs provide the interface between the pins of the package and the CLBs. FPGAs are widely used as a prototype before fabricating a VLSI design, or can be used directly in a product. Figure 3.2 shows the basic structure of Xilinx SRAM-based FPGAs.

Figure 3.2: Basic Structure of Xilinx SRAM-based FPGAs

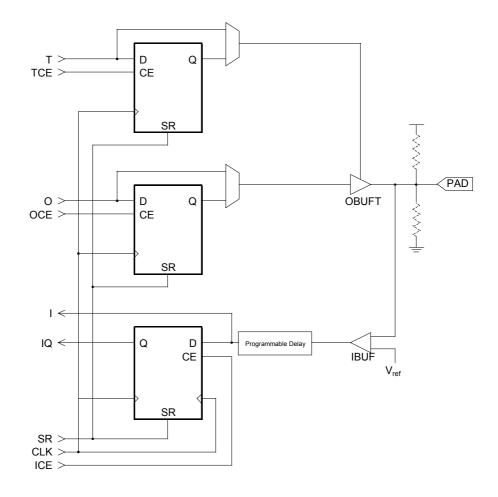

The structure of Xilinx Virtex IOB is shown in Figure 3.3. The three D-type flip-flops are synchronized on the same clock. Two of them are for input and output, and the other one is for the control to the output tri-state buffer. The input signal can be routed to the internal logic either directly or through an input flip-flop. A programmable delay element at the D-input of the input flip-flop is to eliminate the pad-to-pad hold time. Moreover, by configuring the threshold voltage  $V_{ref}$  at the input buffer, the device can support designs with different voltage level. Similarly, the output from the internal logic can be routed to the pad either directly or through the optional output flip-flop. All I/O pins involved in configuration are set to high impedance state so that the internal logic is isolated.

Figure 3.3: Structure of Xilinx Virtex IOB

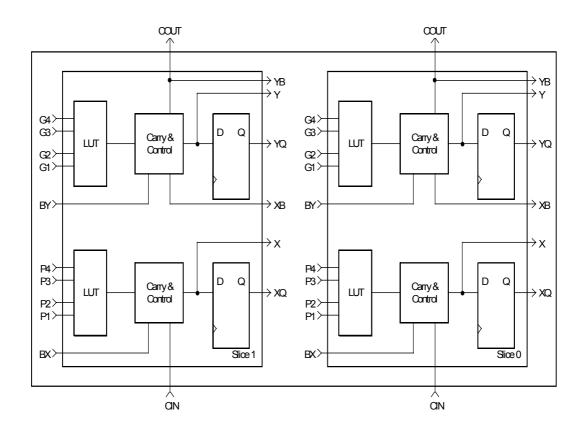

The basic building block of the Xilinx Virtex FPGA is the Logic Cell (LC). A LC includes a 4-input function generator, carry logic and a storage element. Each Virtex CLB contains four LCs, organized in two slices (Figure 3.4). The 4-input function generator are implemented as 4-input look-up tables (LUTs). Each of them can provide the functions of one 4-input LUT or a 16x1-bit synchronous RAM(called "distributed RAM"). Furthermore, two LUTs in a slice can be combined to create a 16x2-bit or 32x1bit synchronous RAM, or a 16x1-bit dual-port synchronous RAM [Xil00].

Figure 3.4: Simplified Structure of Xilinx Virtex CLB

## **Chapter 4**

# **Current SLS SAT Hardware Implementations**

There has been considerable recent interest in the application of FPGAs as accelerators for solving SAT problems. Most previous research on using FPGAs as accelerators for solving SAT problems has concentrated on complete algorithms. Complete algorithms are guaranteed to find a solution if one exists, whereas incomplete algorithms like stochastic local search may not find a solution even if one exist as we have discussed in Chapter 2.

For the complete algorithms, Zhong *et al.* developed a design for SAT problems utilizing the Davis-Putnam algorithm [ZMAM98a] as well as an unimplemented design which used nonchronological backtracking [ZAMM98].

Yokoo et al [YSS96] developed a machine based on FPGAs which implemented a tree search with forward checking for SAT problems. Implementations from Abramovici and Saab [AS97] can also be used to solve for SAT problems. A pathoriented decision making (PODEM) algorithm [Goe81] was used to solve for an encoded SAT problem. This algorithm was developed primarily for Automatic Test-Pattern Generation (ATPG) problems and does not perform quite well with SAT problems. In addition, Suyama et al [SYS98] developed a machine with a dynamic variable ordering heuristic. These approaches are less efficient than the Davis-Putnam procedure as stated in their paper. All of these implementations didn't outperform state of the art DP based algorithms.

Due to the inherent algorithm complexity of the DP SAT algorithm, it is not feasible to extract more parallelism than the implementation in [ZMAM98a]. Our research will focus on the FPGA implementations of WalkSAT algorithms which is a robust family in stochastic local search. In this chapter, we first review two recent implementations of GSAT [HTY01] and WalkSAT [Tan02]. These two implementations can achieve "one flip per clock cycle" performance. After that, another two implementations for GSAT [YSLL99] and WalkSAT from [LSW01] are discussed.

### 4.1 One Flip per Clock Cycle for GSAT

This section reviews the implementation of GSAT given by Henz, Tan, and Yap [HTY01]. In their work, they showed how GSAT can be implemented to be as fast as possible in hardware. Their implementation using FPGA achieves one flip per clock cycle by exploiting maximal parallelism and at the same time avoiding excessive hardware cost in terms of gates.

The speed of the GSAT implementations given in Hamadi and Merceron [HM97] and Yung et al. [YSLL99] is limited, because only clause evaluation is parallelized but variable scoring is not, hence the minimal depth of CHOOSE\_FLIP after applying pipelining will still have a factor of n (n is the number of variables).

In the algorithm shown in Figure 2.2, Henz *et al.* found that there is no dependency between the score computation of different variables. Thus, this is

obviously another parallelism opportunity. Figure 4.1 shows this naive maximum parallelism strategy.

```

procedure CHOOSE_FLIP(f, V, cnf)

output: variable f that produces the maximum score

par (for i := 1 to n ) do /* for all variables */

scores[i] := scoref(i, cnf, V);

end

return CHOOSE_MAX(scores);

end

```

Figure 4.1: Basic CHOOSE\_FLIP Design with Parallelized Variable Scoring

In Figure 4.1, with key word **par**, the algorithm compute *scoref* [1] to *scoref* [n] in parallel. The depth of the this algorithm is O(log m) (m : the number of clauses), since the *scoref* computation is bounded by O(log m + log n), the CHOOSE\_MAX computation is bounded by O(log n), and we assume n < m. While this is closer to achieving their goal, the drawback is that the cost in gate increases by a factor of n to  $O(mn^2)$ . With the exception of small problems, this design will not be practical.

In [HTY01], they turned to an alternative hardware design. The ideas are related to the software optimizations for GSAT but the rationale is to decrease the circuit size while keeping parallel score evaluation. The key observations are:

- 1. The selection of the flip variable can be done on the basis of relative contribution to the score of that variable when flipped.

- 2. The number of clauses which will be affected by a change to one variable is small and typically bounded.

In [HTY01], Henz *et al.* developed a new procedure as shown in Figure 4.2. As only the affected clauses should be referred, function  $score_{C}(i, cnf_{C}(i), V)$  and function  $score_{C}(i, cnf_{C}(i), V'[\neg V(i)/i])$  are used. Function  $score_{C}(i, cnf_{C}(i), V)$  returns the number of clauses satisfied as a result of using a variable assignment V in  $cnf_{C(i)}$ , while function  $score_{C}(i, cnf_{C(i)}, V'[\neg V(i)/i])$  returns the number of clauses satisfied as a result of using a new variable assignment  $V'[\neg V(i)/i]$ . The new variable assignment  $V'[\neg V(i)/i]$  is generated from the old variable assignment V when V is changed with the *i*-the variable is flipped. The notation  $cnf_{C(i)}$  represents the set of clauses which contain variable *i*. For a particular SAT problem,  $cnf_{C(i)}$  is constant. Thus, for each variable *i*, a fixed Boolean function can be extracted from  $cnf_{C(i)}$  in order to get OldS[i] and NewS[i].

The bound on the maximum number of clauses per variable can be denoted by *MaxClauses*. In practice, most SAT problems have also a bound on the number of variables per clause, which can be denoted by *MaxVar*. For example, for 3-SAT, *MaxVars* is 3. Thus, the number of gates for procedure in Figure 4.2 is O(MaxVars MaxClauses n). The depth for it is O(log MaxClauses + log MaxVars), which for practical SAT problems is much smaller than O(log m). One more advantage of their design is that the circuit for  $score_c$  is also smaller because the actual size of the numbers to be considered requires less bit.

| procedure CHOOSE_FLIP( <i>f</i> , <i>V</i> , <i>cnf</i> )                   |

|-----------------------------------------------------------------------------|

| output: variable f that produces the maximum score                          |

| <i>s1</i> : <b>par</b> (for $i := 1$ to $n$ ) do /* for all variables */    |

| $NewS[i] := score_{\mathcal{C}}(i, cnf_{\mathcal{C}}(i), V'[\neg V(i)/i]);$ |

| end                                                                         |

| s1: <b>par</b> (for $i := 1$ to $n$ ) do /* for all variables */            |

| $OldS[i] := score_{\mathcal{C}}(i, cnf_{\mathcal{C}}(i), V);$               |

| end                                                                         |

| s2: <b>par</b> (for $i := 1$ to $n$ ) do /* for all variables */            |

| Diff[i] := NewS[i] - OldS[i];                                               |

| end                                                                         |

| $s3$ : $f := CHOOSE\_MAX(Diff);$                                            |

| end                                                                         |

Figure 4.2: Parallel CHOOSE\_FLIP with Relative Scoring

With the above procedure the innermost loop of GSAT is over flips. Unfortunately, it is not possible to pipeline the different flip iterations of CHOOSE\_FLIP, since each iteration is dependent on the flip of the previous iteration. Instead, pipelining the outer loop of the procedure show in Figure 2.1 is available, which is called multi-try pipelining in [HTY01]. Since there is no dependency between different tries in GSAT, essentially one can parallelize each try independently. Each pipeline stage deals in parallel with the work for a different try. For simplicity, *maxtries* should be a multiple of the number of stages in the pipeline.

In practice, in the actual implementation it is feasible in one clock cycle to accommodate the  $score_c$  for all variables. Therefore, to achieve one flip per clock cycle for GSAT is only need to allocate each design block in the procedure in Figure 4.2 to a pipeline stage *s*, leading to a pipeline with four stages. The first three stages, *s1* to *s3* are labeled in the procedure in Figure 4.2. The last stage, *s4*, which is not in the CHOOSE\_FLIP procedure, is the circuit to make actual flip. This is illustrated in Figure 4.3, where procedure in Figure 4.2 is implemented as a four-stage pipeline which gives one flip per clock cycle.

| Tries | time1 | time2 | time3 | time4 | time5 | time6     | time7 | time8 |  |

|-------|-------|-------|-------|-------|-------|-----------|-------|-------|--|

| Try1  | sl    | s2    | s3    | s4    | s1    | <i>S2</i> | s3    | s4    |  |

| Try2  |       | s1    | s2    | s3    | s4    | S1        | s2    | s3    |  |

| Try3  |       |       | s1    | s2    | s3    | <i>S4</i> | sl    | s2    |  |

| Try4  |       |       |       | s1    | s2    | S3        | s4    | s1    |  |

Figure 4.3: A Four Stage Pipeline for GSAT

# 4.2 One Flip per Clock Cycle for WalkSAT

In this section, we review another FPGA-based implementation which is of WalkSAT algorithm and also achieved one flip per clock cycle in [Tan02].

The WalkSAT algorithm is technically an offspring of a GSAT variant, GSAT with random walk [SKC94]. For this reason, Tan *et al.* [Tan02] adapted many implementation details from GSAT in [HTY01] which is reviewed in the previous section. The algorithm they used is as the procedure shown in Figure 2.3, and they set the noise parameter N to 0%.

WalkSAT uses a function *scoreb* that counts for the number of clause that will be unsatisfied when a variable is flipped. It is found that the clause evaluation as the procedure in Figure 4.1 is ideal for a fast WalkSAT solver design. For GSAT, the procedure in Figure 4.1 is truly impractical due to the large size increase to a factor of n. But for a WalkSAT implementation of a 3-SAT problem, the increase of the hardware size is only a factor of 3.

Figure 4.4 shows the complete instance-specific WalkSAT hardware design in [Tan02]. The main computation is divided into six data dependent stages, labeled sI to s6. In stage s1, the function CHOOSE\_ONE selects one unsatisfied clause c from Cp using uniform distribution; Cp contains the sequence of unsatisfied clauses from the last iteration. This stage also determines whether the last iteration has produced a satisfying solution; all the clauses are satisfied when SUM(Cp) is equal to zero. For the next stage s2, the VARIABLE\_LIST(Vp, j, i) returns the variable sequence V'p with the *i*-th variable in clause j inverted. It is assumed that there are three variables per clause, therefore, there are V[1], V[2], V[3] to store the variable assignments with different variable flipped. The next stage s3 evaluates the variable assignments to the cnf and then forms a list of unsatisfied clauses for each of the variable assignments. Stage s4 computes for the  $score_b$  for each of the three variable assignments (Function  $score_b$  is discussed in Section 2.2). The next stage s5 determines the variable assignment that produced the least  $score_b$ . In the next stage s6, the new variable

assignment will be updated, as well as the list of unsatisfied clauses. This loop would repeat until a satisfying solution is found or the *maxflips* number of iterations is reached.

| MAIN       |                                                        |

|------------|--------------------------------------------------------|

|            | $V_p := \text{RECEIVE_INITIAL_ASSIGNMENT()};$          |

|            | $C_p := \{1: j \in [1m]\};$                            |

| s1:        | for $i := 1$ to maxflips do                            |

| 81.        | par{<br>if SUM(C <sub>p</sub> ) = 0 then BREAK;        |

|            | $c := CHOOSE_ONE(C_p);$                                |

|            | };                                                     |

| s2:        | par{                                                   |

|            | $V[1] := VARIABLE\_LIST(V_p, c, 1);$                   |

|            | $V[2] := VARIABLE\_LIST(V_p, c, 2);$                   |

|            | $V[3] := VARIABLE\_LIST(V_p, c, 3);$                   |

|            | };                                                     |

| s3:        | par{                                                   |

|            | $C[1] := \{\neg \text{EVAL}_j(V[1]) : j \in [1m]\};$   |

|            | $C[2] := \{\neg \text{EVAL}_{j}(V[2]) : j \in [1m]\};$ |

|            | $C[3] := \{\neg \text{EVAL}_{j}(V[3]) : j \in [1m]\};$ |

|            | }                                                      |

| s4:        | par{                                                   |

|            | $S[1] := \text{SUM}(\neg C_p \land C[1]);$             |

|            | $S[2] := \text{SUM}(\neg C_p \land C[2]);$             |

|            | $S[3] := \text{SUM}(\neg C_p \land C[3]);$             |

| ~          |                                                        |

| s5:<br>s6: | <pre>i := OBTAIN_MIN_INDEX(S); par{</pre>              |

| 50.        | $par \{ V_p := V[i]; $                                 |

|            | $C_p := C[i];$                                         |

|            | }                                                      |

|            | end;                                                   |

|            | SEND_ASSIGNMENT( $V_p$ )                               |

|            | -                                                      |

|            |                                                        |

Figure 4.4: Instance Specific Implementation of the WalkSAT Algorithm

As we can see from the procedure in Figure 4.4, the innermost loop of WalkSAT is also over flips. Just like the implementation of GSAT, it is impossible to pipeline the different flip iterations of CHOOSE\_FLIP since the data dependency between the consecutive flips. Instead, pipelining the outer loop of the procedure show in Figure 2.1 is also available for WalkSAT, which is called multi-try pipelining in [HTY01]. Since there is no dependency between different tries in WalkSAT, essentially one can parallelize each try independently, in this way, one flip per clock cycle for WalkSAT is achieved.

### 4.3 GSAT Variant by Yung et al.

In this section, we will review another FPGA-based GSAT implementation which was given by Yung *et al.* [YSLL99].

Although the implementations discussed in section 4.1 and 4.2 can run at one flip per clock cycle and can get performance gains of about two orders of magnitude over software, their approach are not practical as a general SAT problem solver, because the time to re-synthesize, place and route the new design for a new SAT problem is likely to significantly exceed the runtime improvement from the faster solvers. In section 4.3 and 4.4, we will review two implementations which address this problem.

From 1999, bitstream reconfigurable systems have been employed to address the re-synthesis problem occurring in instance-specific implementations for solving SAT problems. In [YSL99], Yung *et al.* provide a method of modifying the bitstream in a problem specific fashion without requiring re-synthesis. Like [ASS99], the runtime configurable systems in [YSL99] also used Xilinx XC6200 series devices [Xil6200] which document the manner in which the bitstream relates to the hardware of the device. However, XC6200 devices have been discontinued by Xilinx and also have

very small logic capability (The largest reported bitstream reconfigurable system only supports 13 variables and 29 clauses [ASS99].).

The difference in the work by Yung et al. [YSLL99] is the use of partial resynthesis of the design that bypasses the synthesis. Their design technique is only possible with two assumptions. First, the device vendor like in their case Xilinx Inc. has provided enough information to reconstruct their configuration file for the Xilinx XC6216 FPGA. Secondly, the changes to their design should be simple and should do not affect the timing constraints

Yung *et al.* was able to provide partial reconfiguration to the FPGA given the advantage of knowing how to construct the configuration file. Their approach allows reconfiguration that skips the synthesis tool and allows directly changing the configuration of the FPGA. Current FPGA chips do not provide an open architecture thus rendering this technique useless. Xilinx has currently announced that they would release future FPGA chips that would allow partial reconfiguration. Partial reconfiguration will allow CLB rows to be configured separately and could reduce synthesis time by a factor. This technology has yet to come out and it would improve the performance of instance-specific design implementation.

Since the algorithm used in [YSLL99] was patterned after the algorithm provided by Sleman, Levesque and Mitchell in [SLM92] rather than the optimized version as in GSAT41 [Hoo96], the respondent FPGA-based implementation in [YSLL99], like that in [HM97], was not fully parallelized. Thus the implementation in [YSLL99] didn't provide enough performance increase compared with the GSAT implementation we discussed in the previous section which significantly improved over GSAT41 running on fast CPUs.

### 4.4 WalkSAT based on ROM Array

In 2001, Leong *et al.* [LSW01] achieved a bitstream reconfigurable FPGA implementation for WalkSAT. The algorithm they adopted is as the procedure shown in Figure 2.3. In their implementations, the noise N is set to 100%. Their implementation stores clauses for a SAT problem in the 16x1-bit ROM available in the Logic Cells (LCs) of the Xilinx FPGA. A different SAT instance requires various ROM definitions to be modified. Normally this would require re-synthesis of the FPGA to generate a new bitstream configuration for downloading. Leong *et al.* were able to achieve an implementation without requiring re-synthesis by designing a transformer for the ROM configuration.

In their scheme, the circuit is designed in the normal fashion and the ROMs can be placed at arbitrary locations. After synthesis, technology mapping, placing and routing, a circuit description file (for the Xilinx tools, this file has an extension *.ncd* which means Native Circuit Description.) is generated. This file can be opened with Xilinx tool *FPGA Editor*. *FPGA Editor* is a graphical application for displaying and configuring FPGAs. The *FPGA Editor* can read from and write to NCD files, macro files (NMC), and Physical Constraints Files (PCF). Under the environment of *FPGA Editor*, the names and physical locations of those LCs, by which the ROM arrays of the clause checker are implemented, can be found.

At the same time, with another kind of Xilinx tool named *ncd2xdl*, the binaryformat bitstream file *.ncd*, which stores the contents of the circuit, can be converted into a human readable format, and then, with the information regarding the names and the physical locations of the LCs of the ROM array acquired under *FPGA Editor*, data stored in these LCs can be extracted and modified. In [LSW01], a program was written which takes as input the normal *.ncd* file and the specification of a specific SAT problem in the standard DIMACS benchmark format [DIMACS]. For each SAT problem, this transformer designed modifies the bitstream *.ncd* file according to the SAT problem specification by customizing the ROM values and recomputed the Cyclic Redundant Check (CRC) of the *.ncd* file. After that, the resulting bitstream file *.bit* generated by Xilinx tool *bitgen* can be downloaded to a Virtex FPGA to find a solution for this SAT problem instance.

In their scheme, they elect to recalculate the CRC checksum inside their software transformer. In this way, they can avoid running the Design Rules Checker (DRC) when recreating the configuration *.bit* file. CRC bits are checksum bits that the FPGA uses to verify that the bitstream transmitted correctly.

This approach requires analysis of the bitstream *.ncd* file to figure out how to rebuild the configuration without re-synthesis. Like [YSLL99], the implementation in [LSW01] simulates re-synthesis in a very efficient fashion. However, it is also dependent on the ability to modify the FPGA configuration.

# Chapter 5

# **Clause Evaluator without Re-Synthesis**

Instance specific implementations for SAT problems have provided an outstanding performance from their compact sizes. This is achieved by using a customized design that is specific for each problem. The disadvantage of these implementations is that a high level description of a circuit customized for a particular SAT problem is needed. In order to execute the design, an entire iteration of the synthesis, map, place and route (P&R) cycle was required for each problem. These steps are time consuming (it can take several hours to synthesize, map, place and route a large design.) and preclude their use in real time systems. Our goal is to develop a general system which avoids these steps. We develop a general clause evaluator for WalkSAT solvers, which fits well within an FPGA architecture and can be reconfigured according to different SAT problems quickly in a portable fashion. In this Chapter, Section 5.1 discusses the compilation (synthesis) time on current platform in order to demonstrate the shortcoming of the instance-specific implementations. Section 5.2 describes our general clause evaluator.

### 5.1 Compilation Time on Current Platform

For instance-specific designs, since the circuit is generated according to the specific SAT problem to be solved, the problem solving time should take into account compilation time. In this section, we investigate the actual compilation time for instance-specific designs by reviewing the implementations which achieved one flip per clock cycle in [Tan02]. These implementations are based on GSAT and WalkSAT strategies respectively.

As shown in Table 5.1 and Table 5.2, for instance-specific implementations using FPGAs, the following steps contribute to the total compilation time.

**1. Handel-C Synthesis (Syn):** This is a process called logic synthesis which compiles a Handel-C project into a Electronic Design Interface Format (EDIF) netlist file. EDIF netlist is a standard netlist format which describes a circuit including the basic elements and their connections. This process takes the Handel-C project as input and then generates the circuit structure implementing the functions described in the Handel-C.

**2. Xilinx mapping (Map):** The EDIF netlist uses generic constructs to describe the circuit while the FPGAs have their own logic functional units. For example, a netlist can express combinational circuits in terms of AND, OR and inverter gates. The target FPGA uses the CLBs to realize logic functions. Fitting the logic gates into the LUTs in the CLBs is called technology mapping. After mapping, the circuit is represented by the functions of the CLBs and the routing newtwork between these CLBs.

**3. Xilinx placement and routing (Par):** This is the placement and routing of physical design. The task of placement is to determine the location of the

logic functions on the target FPGA. The placement of the logic functions should facilitate later routing. A good placement should minimize the routing congestion and routing delay. Typically, placement is optimized through iterative improvement after an initial constructive placement. With the logic elements in place, routing takes care of creating the connections between these elements. Since the routing resources are limited, there is no guarantee that a circuit can be routed. It may take several tries to get an acceptable routing.

**4. Xilinx bitstream generation (Bitg):** After the logic functions and routing are all determined, Xilinx's bitstream generation program, BitGen, takes a fully routed circuit description file as its input and produces a configuration *bitstream* – a binary file. This *bitstream* file contains all of the configuration information.

**5. Download configuration:** This process download the bitstream file into the FPGA's memory cell. On our current AMD Athlon 1.2GHz CPU it takes about 0.14 seconds or so.

| SAT Problems       | Var | Cla | Slices | Syn   | Map   | Par   | Bitg  | Total |

|--------------------|-----|-----|--------|-------|-------|-------|-------|-------|

|                    |     |     |        | (min) | (min) | (min) | (min) | (min) |

| uf20-01            | 20  | 91  | 17%    | 10    | 1     | 2     | 2     | 15    |

| aim-50-1_6-yes1-1  | 50  | 80  | 18%    | 10    | 1     | 1     | 2     | 14    |

| aim-50-2_0-yes1-1  | 50  | 100 | 20%    | 13    | 1     | 2     | 2     | 18    |

| aim-50-3_4-yes1-1  | 50  | 170 | 31%    | 40    | 3     | 3     | 2     | 48    |

| aim-50-6_0-yes1-1  | 50  | 300 | 54%    | 171   | 6     | 6     | 2     | 185   |

| aim-100-1_6-yes1-1 | 100 | 160 | 34%    | 43    | 3     | 4     | 2     | 52    |

| aim-100-2_0-yes1-1 | 100 | 200 | 40%    | 63    | 5     | 4     | 2     | 74    |

| aim-100-3_4-yes1-1 | 100 | 340 | 64%    | 199   | 11    | 14    | 2     | 226   |

| flat30-01          | 90  | 300 | 57%    | 198   | 7     | 8     | 2     | 217   |

| BMS_k3_n100_m429_0 | 100 | 286 | 56%    | 199   | 7     | 8     | 2     | 216   |

| RTI_k3_n100_429_0  | 100 | 429 | 79%    | 293   | 19    | 12    | 2     | 326   |

| uf50-01            | 50  | 218 | 39%    | 55    | 5     | 3     | 2     | 65    |

| uf100-01           | 100 | 430 | 89%    | 294   | 19    | 12    | 2     | 327   |

Table 5.1: Time Spent on Re-synthesis for GSAT in Section 4.1

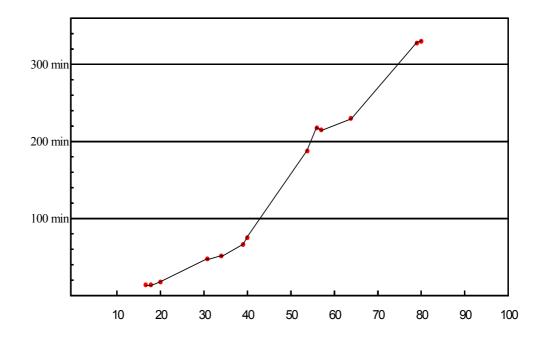

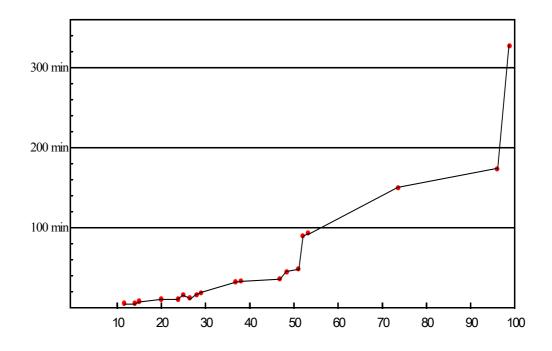

Table 5.1 shows the time spent on these steps for different problems for instancespecific one flip per clock cycle implementation for GSAT achieved in [HTY01]. Table 5.2 shows the time spent on the re-synthesis steps for different problems for the instance-specific one flip per clock implementation for WalkSAT achieved in [Tan02].