## **Model-driven Timing Analysis of Embedded Software**

#### LEI JU

(B.Eng (HONS), National University of Singapore, Singapore)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

DEPARTMENT OF COMPUTER SCIENCE

NATIONAL UNIVERSITY OF SINGAPORE

2010

# **Acknowledgements**

This thesis would not have been possible without the help, support and patience of my supervisors, Prof. Abhik Roychoudhury and Prof. Samarjit Chakraborty. Prof. Abhik Roychoudhury has been my supervisor for over six years, since I was doing my Final Year Project as an undergraduate student in School of Computing, National University of Singapore. During the five years of my graduate study, I have received immense support both in academics and life from Prof. Abhik Roychoudhury and Prof. Samarjit Chakraborty. Their profound knowledge and professional guidance have been of great value to me in my past research work presented in this thesis, and future career in life.

I wish to express my warm and sincere thanks to Prof. Wong Weng Fai and Prof. Chin Wei Ngan as my thesis committee members. They have given me many insightful comments and advices. I have been benefitted a lot from Prof. Tulika Mitra through research collaborations, as well as her distinguished courses on embedded systems. I would also like to thank Prof. Björn Lisper for taking time out of his schedule and agreeing to be my thesis external examiner.

It is an honor for me to join IBM Research - Tokyo as a student intern during my graduate study. I have gained valuable experiences by being exposed to industry-

oriented research work, under the supervision of Dr. Arquimedes Canedo, Dr. Takeo Yoshizawa, and Dr. Hideaki Komatsu.

I dedicate this thesis to my parents that have brought me so much love and encouragement throughout my life. They have been always supportive of me in pursuing my dreams and help me become the person I am today.

I would also like to express my special thanks to Huynh Bach Khoa and Liang Yun, who are great friends in daily life and excellent partners in research collaborations. Besides, I really appreciate the support and friendship from my fiends inside and outside the university, including my lab mates Wang Tao, Guo Liang, Ankit Goel, Vivy Suhendra, Qi Dawei, and Wang Chundong. I thank my basketball team members Prof. Ooi Beng Chin, Yang Fei, Bao Zhifeng, Wu Sai, Zhang Zhenjie, Cao Yu, Zhang Dongxiang, just to name a few. Doing sports with them is of huge fun and has made me refreshed after the tiredness and stress of work.

The work presented in this thesis was partially supported by National University of Singapore research projects R252-000-286-112 and R252-000-321-112. They are gratefully acknowledged.

# **Contents**

| A        | vledgements                   | i                                      |     |  |  |  |

|----------|-------------------------------|----------------------------------------|-----|--|--|--|

| Contents |                               |                                        |     |  |  |  |

| Al       | Abstract Related Publications |                                        |     |  |  |  |

| Re       |                               |                                        |     |  |  |  |

| Li       | List of Tables                |                                        |     |  |  |  |

| Li       | st of l                       | Figures                                | xii |  |  |  |

| 1        | Intr                          | oduction                               | 1   |  |  |  |

| 2        | Bacl                          | kground                                | 9   |  |  |  |

|          | 2.1                           | Design Models                          | 9   |  |  |  |

|          |                               | 2.1.1 The Synchronous Language Esterel | 10  |  |  |  |

|          |                               | 2.1.2 Message Sequence Charts          | 14  |  |  |  |

|          | 2.2                           | Timing Analysis                        | 18  |  |  |  |

|   |      | 2.2.1                                | WCET Analysis                                    | 18 |

|---|------|--------------------------------------|--------------------------------------------------|----|

|   |      | 2.2.2                                | Schedulability Analysis                          | 22 |

| 3 | Rela | ited Wo                              | rk                                               | 27 |

|   | 3.1  | WCET                                 | Analysis for Synchronous models                  | 27 |

|   |      | 3.1.1                                | High-level WCET analysis                         | 28 |

|   |      | 3.1.2                                | Code-level WCET analysis                         | 29 |

|   |      | 3.1.3                                | Timing analysis for special-purpose architecture | 31 |

|   | 3.2  | Schedu                               | ulability Analysis for Distributed System        | 32 |

| 4 | Dowf |                                      | o Dobygging of Estavol                           | 35 |

| 4 | Peri | ormanc                               | re Debugging of Esterel                          | 33 |

|   | 4.1  | Overvi                               | ew                                               | 36 |

|   | 4.2  | Infeasi                              | ble Path Patterns                                | 38 |

|   | 4.3  | SCFG-level Infeasible Path Detection |                                                  |    |

|   |      | 4.3.1                                | Detection of Infeasible Paths Type 1-3           | 44 |

|   |      | 4.3.2                                | Detection of Infeasible Paths Type 4             | 46 |

|   | 4.4  | Infeasi                              | ble Path Elimination                             | 49 |

|   | 4.5  | Perform                              | mance Debugging and WCET Refinement              | 51 |

|   | 4.6  | Experi                               | mental Results                                   | 56 |

|   |      | 4.6.1                                | Experiment Setup                                 | 56 |

|   |      | 4.6.2                                | WCET Analysis Results                            | 58 |

|   |      | 4.6.3                                | Case Study in Performance Debugging              | 59 |

|   | 4.7  | Summa                                | ary                                              | 61 |

| 5 | Context-sensitive Timing Analysis of Esterel |                                          |     |  |

|---|----------------------------------------------|------------------------------------------|-----|--|

|   | 5.1                                          | Overview                                 |     |  |

|   | 5.2                                          | Tick Transition Automata                 |     |  |

|   |                                              | 5.2.1 Formal Definition                  | 66  |  |

|   |                                              | 5.2.2 Construction of TTA                | 68  |  |

|   | 5.3                                          | Inter-tick Control Flow Context          |     |  |

|   | 5.4                                          | Inter-tick Micro-architectural Contexts  |     |  |

|   | 5.5                                          | WCRT Estimation                          |     |  |

|   | 5.6                                          | Case Study                               | 79  |  |

|   | 5.7                                          | Summary                                  | 82  |  |

| 6 | Mul                                          | tiprocessor Execution of Esterel         | 83  |  |

|   | 6.1                                          | Overview                                 |     |  |

|   | 6.2                                          | Code Generation                          |     |  |

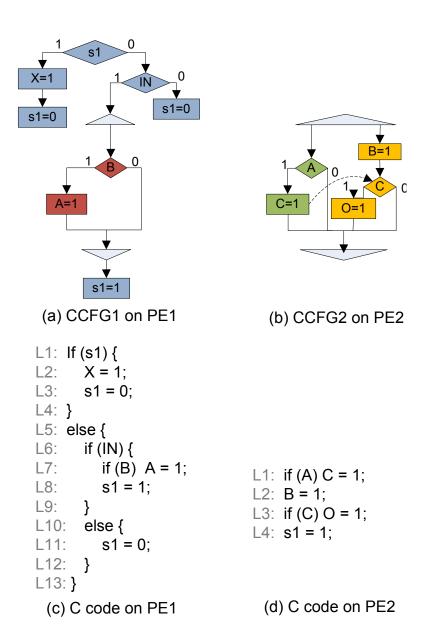

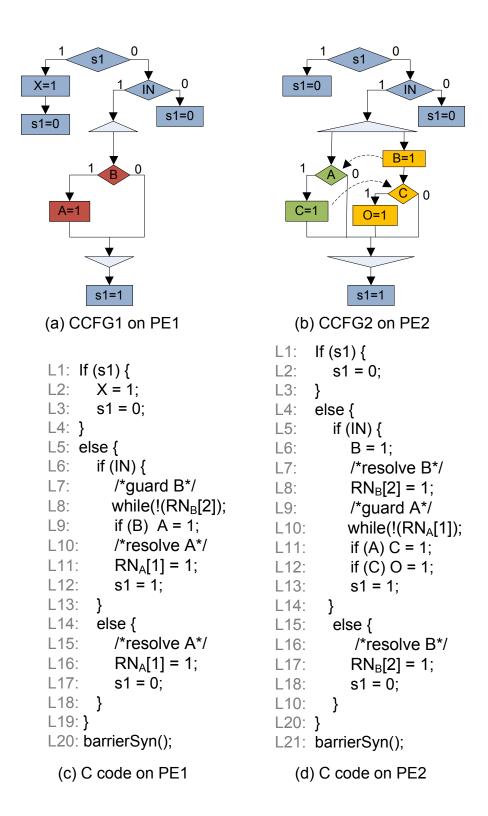

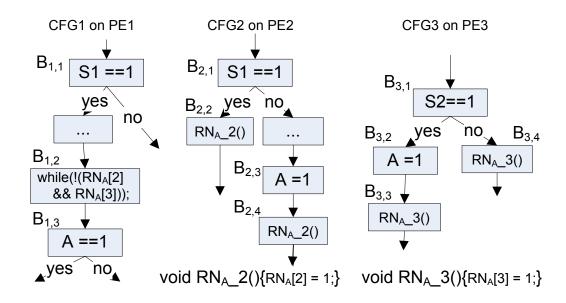

|   |                                              | 6.2.1 Replicating Control-flow           | 89  |  |

|   |                                              | 6.2.2 Handling Signal Communication      | 92  |  |

|   |                                              | 6.2.3 Sequentializing Concurrent Threads | 93  |  |

|   | 6.3                                          | Timing Analysis                          |     |  |

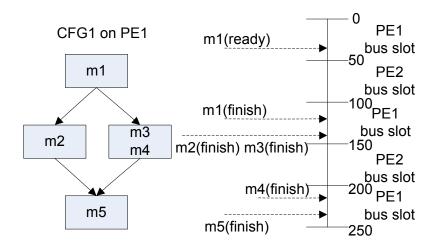

|   |                                              | 6.3.1 Computing Start Times              | 96  |  |

|   |                                              | 6.3.2 Inter-processor Infeasible Paths   | 98  |  |

|   |                                              | 6.3.3 WCET Calculation of a Basic Block  | .00 |  |

|   |                                              | 6.3.4 WCRT Analysis                      | .03 |  |

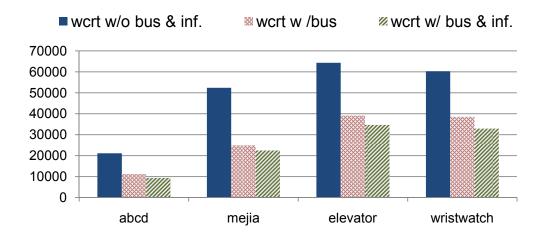

|   | 6.4                                          | Experimental Results                     | .05 |  |

|    | 6.5    | Summ                                 | ary                           | 108 |

|----|--------|--------------------------------------|-------------------------------|-----|

| 7  | Scho   | chedulability Analysis for MSC Model |                               |     |

|    | 7.1    | 7.1 Overview                         |                               |     |

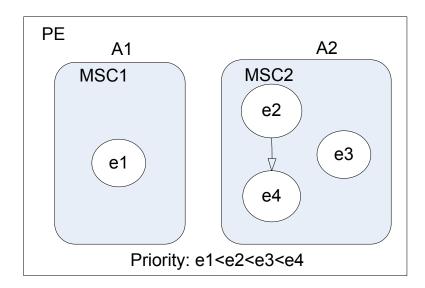

|    |        | 7.1.1                                | Running Example               | 113 |

|    |        | 7.1.2                                | Issues in Analyzing the Model | 116 |

|    | 7.2    | Schedu                               | ulability Analysis Framework  | 119 |

|    | 7.3    | Respon                               | nse Time Calculation          | 123 |

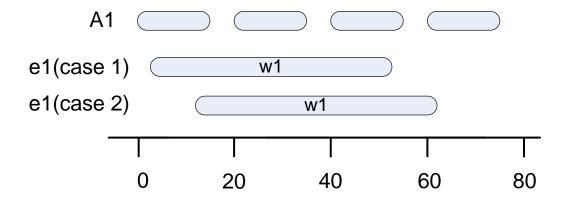

|    |        | 7.3.1                                | Preemption within an MSC      | 125 |

|    |        | 7.3.2                                | Preemption by a Single MSC    | 127 |

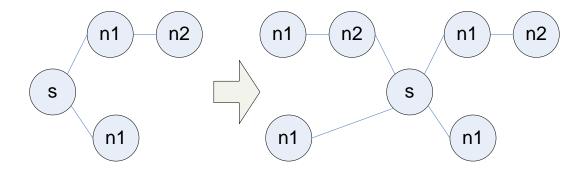

|    |        | 7.3.3                                | Preemption by MSGs            | 134 |

|    | 7.4    | Case S                               | Study                         | 138 |

|    |        | 7.4.1                                | Experimental Setup            | 138 |

|    |        | 7.4.2                                | Experimental Results          | 140 |

|    |        | 7.4.3                                | Discussion                    | 142 |

|    | 7.5    | Summ                                 | ary                           | 143 |

| 8  | Con    | clusion                              | and Future Work               | 144 |

|    | 8.1    | Thesis                               | Contributions                 | 144 |

|    | 8.2    | Future                               | Work                          | 146 |

| Bi | bliogi | raphy                                |                               | 149 |

## **Abstract**

In recent years, model-based design has become an industrial standard to address problems associated with designing complex embedded software. For hard real-time system domains including avionics and automobiles, static timing analysis is of paramount importance. To reinforce the advantages of model-based design approach, timing analysis must be seamlessly coupled to provide designers with temporal behavior of the system at early design stages. In this thesis, we study various models (applicable at different design levels) and corresponding timing analysis techniques. We show that to achieve correct and accurate timing estimates in model-driven embedded software design, both model-level and micro-architectural information need to be considered in the timing analysis.

Code-level WCET analysis determines worst-case timing behavior of a program on a micro-architecture for all possible inputs. In a model-based design framework, executable code is automatically generated from a high-level model. We show that accurate code-level timing estimates can be achieved by taking into account the high-level information in the timing analysis. We discuss our model-driven WCET analysis in the context of Esterel, a representative synchronous programming model. Our proposed

timing analysis utilizes model-level information to help determining program path and context in the WCET analysis of generated C code from Esterel specification. In addition to strengthening existing WCET analysis approaches for sequential programs with our model-driven techniques, we also propose a framework for timing analysis of multiprocessor execution of Esterel specifications. Experimental results show that our analysis substantially reduces WCET over-estimation.

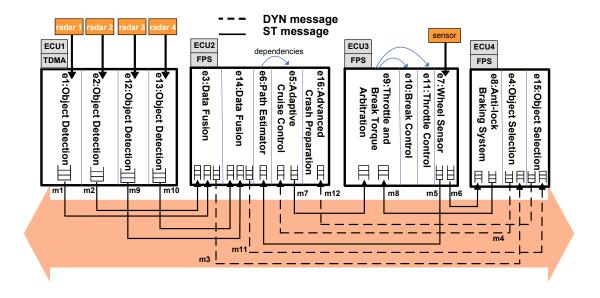

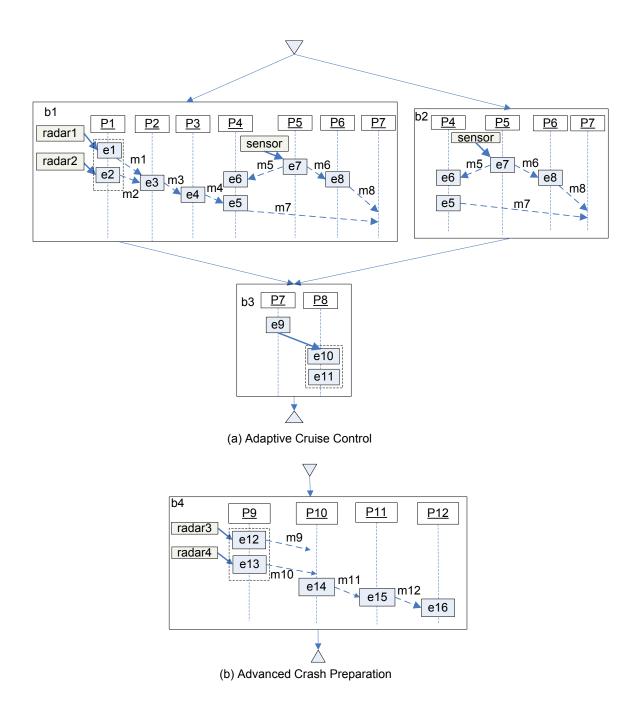

In system-level schedulability analysis, WCET of each individual task is provided as input parameters, which captures the worst-case *intra-task* timing behavior for the task. Traditional task graph-based system models and their schedulability analysis essentially concern with independent tasks and single-processor execution. We propose schedulability analysis for standard Message Sequence Chart (MSC) based system models, which are widely used for describing interaction scenarios between the components of a distributed system. We also capture the timing effects of the shared bus for intertask communication in our proposed analysis. We illustrate the details of our analysis using a setup from the automotive electronics domain, which consist of two real-life application programs (that are naturally modeled using MSCs) running on a platform consisting of multiple electronic control units (ECUs) connected via a FlexRay bus.

## **Related Publications**

- 1. L. Ju. Model-driven Timing Analysis of Embedded Software. *13th ACM SIGDA*PhD Forum at the Design Automation Conference (DAC), 2010.

- 2. L. Ju, B. K. Huynh, A. Roychoudhury, and S. Chakraborty. Timing Analysis of Esterel Programs on General-purpose Multiprocessors. *ACM Design Automation Conference (DAC)*, 2010.

- 3. L. Ju, B. K. Huynh, S. Chakraborty, and A. Roychoudhury. Context-Sensitive Timing Analysis of Esterel Programs. *ACM Design Automation Conference* (*DAC*), 2009.

- 4. L. Ju, B. K. Huynh, A. Roychoudhury and S. Chakraborty. A Systematic Classification and Detection of Infeasible Paths for Accurate WCET Analysis of Esterel Programs. *Singaporean-French IPAL Symposium* (*SinFra*), 2009

- 5. L. Ju, B. K. Huynh, A. Roychoudhury and S. Chakraborty. Performance Debugging of Esterel Specifications. *ACM Intl. Conference on Hardware/Software Codesign and System Synthesis* (*CODES+ISSS*), 2008.

- 6. L. Ju, A. Roychoudhury and S. Chakraborty. Schedulability Analysis of MSC-based System Models. *IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS)*, 2008.

7. L. Ju, S. Chakraborty and A. Roychoudhury. Accounting for Cache-related Preemption Delay in Dynamic Priority Schedulability Analysis. *Design Automation and Test in Europe (DATE)*, 2007.

# **List of Tables**

| 4.1 | Feasible States of the example SCFG shown in Figure 4.3                     |

|-----|-----------------------------------------------------------------------------|

| 4.2 | WCET analysis results                                                       |

| 6.1 | Esterel benchmarks and generated C programs                                 |

| 7.1 | End-to-end delay (from sensor/radar to actuator) for the ACC and ACP appli- |

|     | cations shown in Figure 7.3                                                 |

# **List of Figures**

| 1.1 | Overview of our model-driven timing analysis framework              | 4  |

|-----|---------------------------------------------------------------------|----|

| 2.1 | An example Esterel program                                          | 11 |

| 2.2 | CEC compiler and the intermediate representations                   | 12 |

| 2.3 | An example MSG                                                      | 16 |

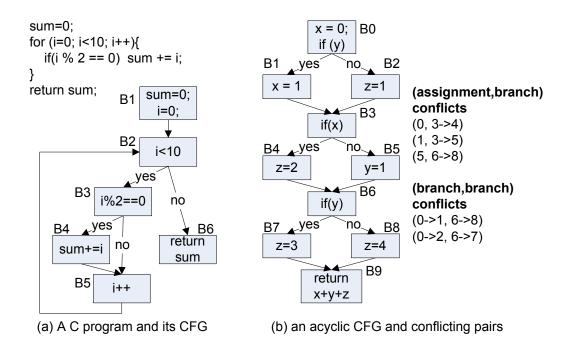

| 2.4 | Example C programs and control flow graphs                          | 19 |

| 2.5 | Relationship between the various task graph based models ([7])      | 23 |

| 2.6 | Examples of Schedulability analysis approaches                      | 25 |

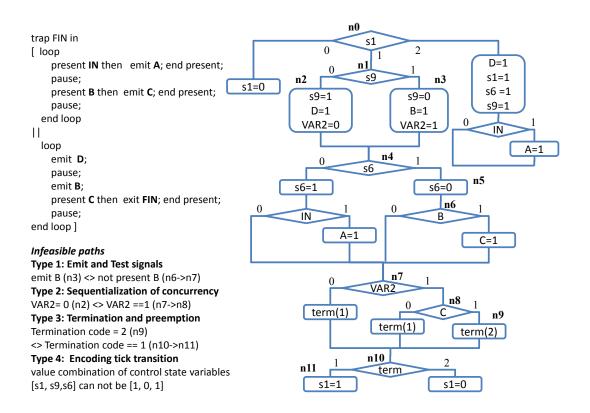

| 4.1 | WCET analysis of a single Esterel tick                              | 36 |

| 4.2 | Example infeasible path patterns in generated C code                | 39 |

| 4.3 | Conflicting pairs in SCFG of an Esterel Program                     | 43 |

| 4.4 | Performance debugging framework for Esterel specifications          | 52 |

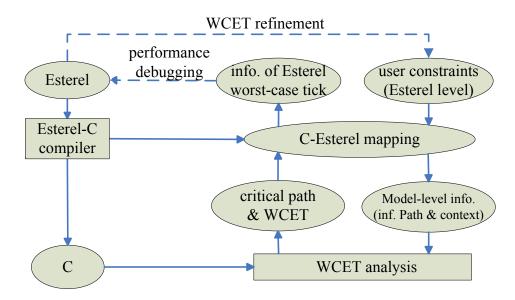

| 4.5 | Construction of the assembly-Esterel mapping in Figure 4.4          | 54 |

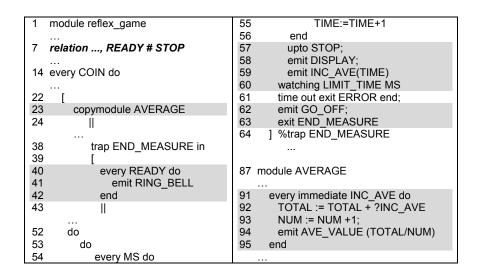

| 4.6 | The reflex game Esterel specification and highlighted critical path | 59 |

| 4.7 | C-level critical path of the reflex game                            | 60 |

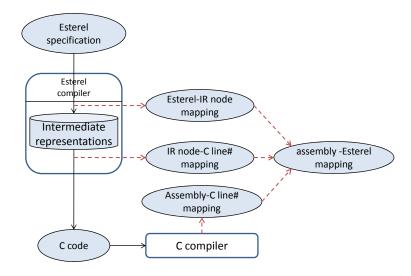

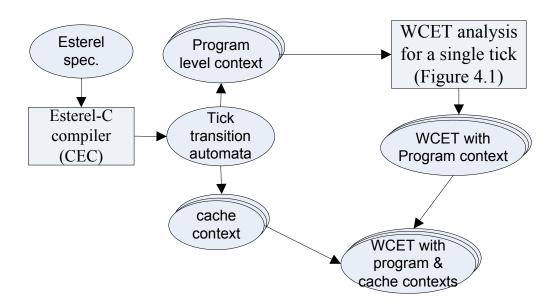

| 5.1 | Context-sensitive timing analysis framework                         | 64 |

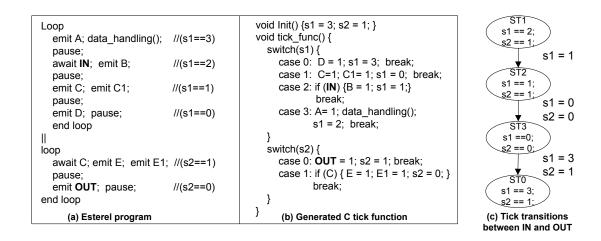

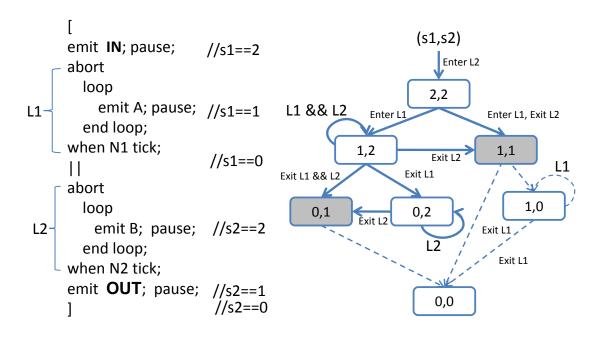

| 5.2 | An Esterel program, compiled C tick function, and tick transitions             | 65  |

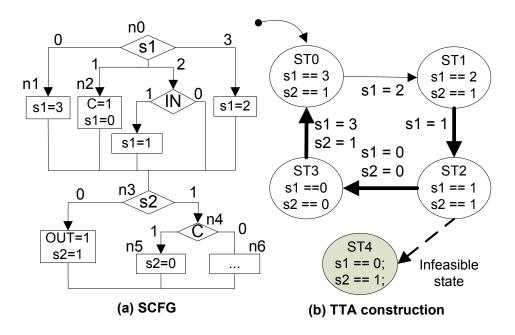

|-----|--------------------------------------------------------------------------------|-----|

| 5.3 | SCFG and TTA construction for the program in Figure 5.2                        | 68  |

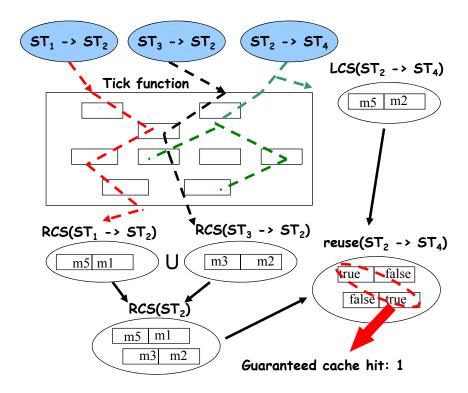

| 5.4 | Example of inter-tick cache reuse analysis                                     | 75  |

| 5.5 | An Esterel program containing loops and its TTA                                | 77  |

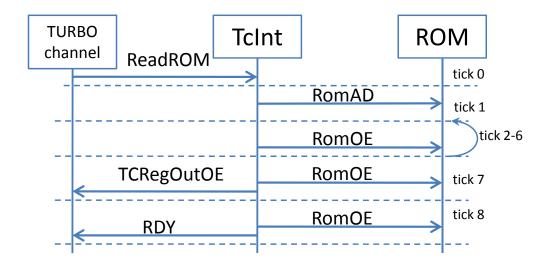

| 5.6 | ROM read operation in TURBOchannel interface program                           | 79  |

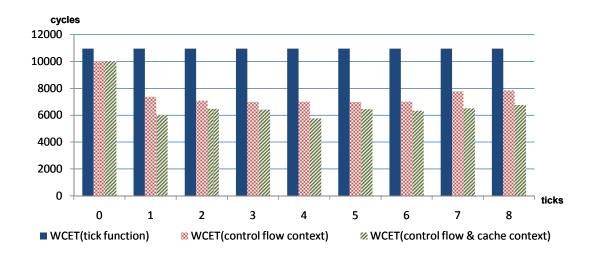

| 5.7 | Tick WCET results from different calculation approaches                        | 81  |

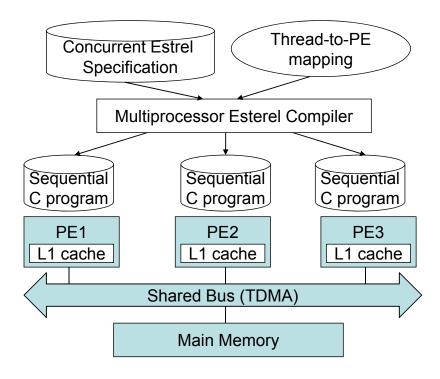

| 6.1 | Multiprocessor execution of Esterel Specification                              | 85  |

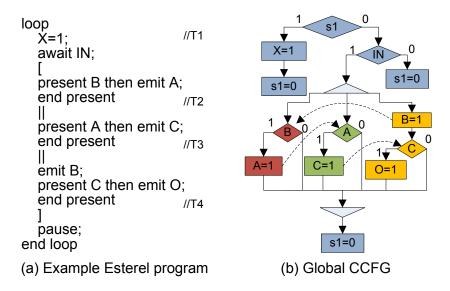

| 6.2 | Example Esterel specification and it concurrent control flow graph (CCFG)      | 86  |

| 6.3 | Incorrect multiprocessor code generation                                       | 87  |

| 6.4 | Correct multiprocessor code generation                                         | 90  |

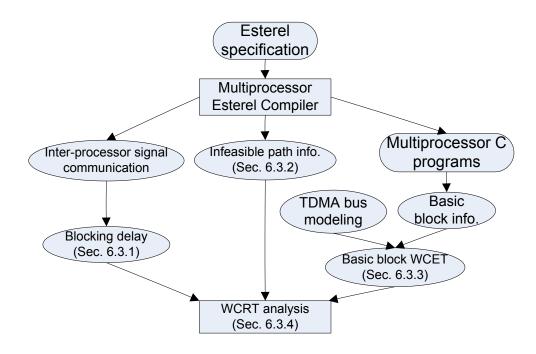

| 6.5 | Overview of timing analysis framework for multiprocessor execution of Esterel. | 95  |

| 6.6 | Blocking delay due to signal communication                                     | 97  |

| 6.7 | Shared TDMA bus modeling                                                       | 102 |

| 6.8 | WCRT analysis results                                                          | 107 |

| 7.1 | Overview of our model-driven timing analysis framework (from Figure 1.1)       | 110 |

| 7.2 | A basic MSC and timing annotations                                             | 111 |

| 7.3 | A FlexRay-based ECU network                                                    | 113 |

| 7.4 | MSG model of the ACC and ACP applications                                      | 114 |

| 7.5 | Overview of our schedulability analysis framework                              | 119 |

| 7.6 | Projection of Events on same PE                                                | 128 |

| 7.7 | Preemption from other applications                                             | 136 |

| 7.8  | Constructing a super preemption graph                                      | 136 |

|------|----------------------------------------------------------------------------|-----|

| 7.9  | Delay bound for ACP obtained using our proposed analysis and the technique |     |

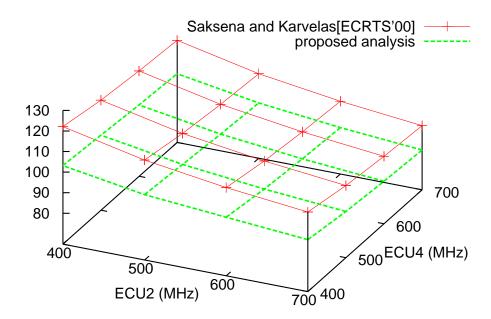

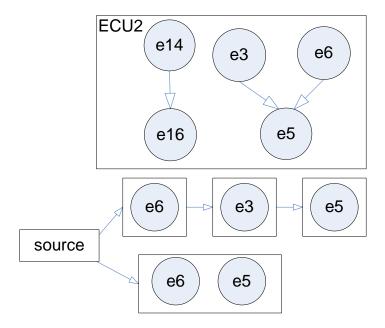

|      | presented in [96]                                                          | 141 |

| 7.10 | Preemption graph for $e14$ by events from the ACC application              | 142 |

# Chapter 1

## Introduction

In recent years, model-based design has become an industrial standard to address problems associated with designing complex embedded software. It provides an efficient and cost-effective way to support various stages in the development cycle, including requirement engineering, design reuse, model-based testing, simulation and verification. Mature commercial tools have been built and are successfully adopted in different application domains, including UML (the Unified Modeling Language) [49], MATLAB Simulink [101] and SCADE Suite [97]. In the model-based design flows, the entire system description is usually developed as high-level models and final hardware/software deployment can be automatically generated from these models (also referred to as model-driven engineering [45]).

Lots of methodologies and tool support have been built for model-driven testing and verification (e.g., [108, 30, 103, 32, 73]). However, a significant portion of the works focus on functionality analysis (such as verification of safety and liveness properties).

On the other hand, very limited effort has been invested to support quantitative/timing analysis in model-based design. Existing model-level software performance predictive analyses ([6]) are based on high-level performance models (e.g., the UML Profile for Scheduling, Performance, and Time [48], and timed automata [2]), where timing information are given and annotated with the model elements. However, such analyses are usually ignorant to the underlying architecture platforms where generated software implementations are executed (which may leads to loose or even unsafe analysis results). Furthermore, a systematic design process for automatic calculation of platform-specific timing information of model elements is missing.

Timing analysis plays an very important role in real-time and embedded system design. Simulation based timing analysis techniques (e.g., [79]) are expensive, and the observed execution time may be an under-estimation of the *real* worst case scenario. In hard real-time domains (e.g., avionics, automobiles and medical embedded devices), guaranteed upper bound of worst-case timing behavior must be provided via static timing analysis to ensure the correctness and safety of a system. Two well-studied static software timing analysis approaches in embedded system design are:

• Code-level worst-case execution time (WCET) analysis. WCET analysis computes the maximum execution time of a program on a micro-architecture for all possible inputs. Accuracy of the estimated WCET depends on both program path information and timing effect of the micro-architecture. Thus, a typical WCET analysis involves code level flow analysis ([66, 53]) and micro-architectural modeling (e.g., pipelines [36, 70], caches [43, 26], and branch predictors [29]).

• System-level schedulability analysis. A schedulability analysis (or feasibility analysis) decides that given a set of tasks and a certain scheduling policy, whether all constraints(usually the deadlines) associated with each task could be satisfied. Various schedulability analysis techniques have been proposed for different task models on single-processor ([74, 9, 82, 8, 7]) or multiprocessor/distributed ([107, 110, 87, 18]) execution.

Motivation of this dissertation: The motivation of this dissertation is to provide seamless timing analysis support for modern model-based design framework of real-time embedded systems. Traditional schedulability analysis techniques are applicable to system models that are essentially based on the concept of task graphs (e.g., [74, 7]). However, such task graph-based models only provide *local* or *processor-centric* views of a system, and are not very suitable for specifying the interactions between the multiple entities of system. Comparing to high-level behavioral modeling languages used in model-based design frameworks(e.g. message sequence charts MSC [58]), such task graph-based specifications are too abstract and lack of expressive power to model all possible behaviors (e.g., data communication, conditional execution) for complex system functionalities.

On the other hand, one significant challenge for static WCET analysis is to reduce the overestimation between estimated WCET and real WCET, due to dynamic program behavior and complexity of underlying architecture. State-of-the-art WCET analysis techniques ([109]) try to achieve accurate timing estimates, by tightly coupling program

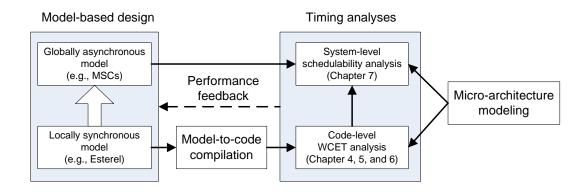

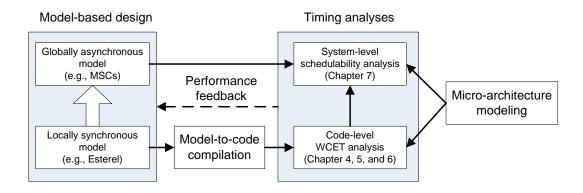

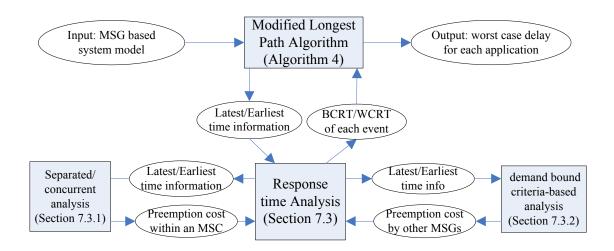

Figure 1.1: Overview of our model-driven timing analysis framework

path analysis (at source/binary code level) and micro-architectural modeling. However, for model-based design framework where source programs are automatically generated from high level models, blindly analyzing the generated code without taking model-level information into consideration may lead to additional overestimation.

Contributions of this dissertation: To achieve our goal, we propose methodologies of both system-level schedulability analysis and low-level WCET analysis for model-based design frameworks. Figure 1.1 presents an overview of our proposed timing analysis for model-driven embedded system design. In this work, we consider a fairly general model hierarchy called the Globally-Asynchronous Locally-Synchronous (GALS) model [25, 83]. Each local task is designed in a synchronous model (e.g., the synchronous language Esterel [21]), where all computation and communication for a set of given inputs and outputs are assumed to react instantaneously. Software implementation (e.g., C programs) can be automatically generated from the synchronous model. The global system is represented with an asynchronous model (e.g., MSCs), which describes relations between individual local tasks of various applications in the system,

including the control/data dependencies and communications. The global system is asynchronous such that (i) reaction time of each local task, as viewed by other tasks is finite and non-zero; and (ii) communication time between local tasks are finite and non-zero.

For timing analysis of the above-mentioned setting, code-level WCET analysis can be performed on code generated from the locally synchronous model of each task. The system-level schedulability analysis determines the satisfaction of timing constraints (e.g., deadlines) annotated on the globally asynchronous model, given the estimated WCET values of individual tasks, as well as other properties including task periods, tasks to processing elements (PEs) mapping, and the architecture configuration. The main contributions of this dissertation are summarized below.

- We propose an accurate WCET analysis framework for C programs generated from Esterel specifications, which have been widely adopted for designing reactive kernels in safety-critical domains such as avionics ([11]). Automatically generated code from high-level control-intensive models like Esterel usually contains massive number of infeasible paths, compared to human-written programs. In our WCET analysis, we can efficiently and effectively identify and remove infeasible paths in the generated code by exploiting the semantics and compilation information of the source Esterel specification. Thus, tighter WCET estimate of a single Esterel tick execution can be obtained ([62]).

- We show that bi-direction traceability can be automatically built between highlevel model and low-level timing analysis [62]. By applying the maintained

model-to-code mapping on the calculated WCET path, we are able to identify parts of the model specification which might pose as timing/performance bottle-necks with respect to the underlying platform. This not only allows a designer to optimize or simplify Esterel specifications, but also choose/configure suitable implementation platforms.

- In [61], we further extend our timing analysis for Esterel specification to capture context information between tick executions. We show that program control flow as well as architecture contexts can be used to rule out certain execution paths and architecture states in the code to be executed within a tick. Our experimental results with realistic case studies show 40% tighter timing estimates when program control flow and inter-tick cache context information is taken into account.

- Following this line of work, we propose a scheme for generating efficient code from Esterel specifications for a multiprocessor execution. Furthermore, we achieve tight timing estimation on the generated multiprocessor C code, by considering inter-processor infeasible program flow and modeling the timing effect of the shared bus ([63]).

- We propose a general schedulability analysis for distributed system modeled in a

globally asynchronous message sequence chart (MSC) based specification ([64]).

MSC graphs (MSGs) can be very convenient for describing interactions among

a number of agents, therefore a natural choice for modeling and specifying distributed real-time and embedded systems. Given a system description in MSGs,

along with the scheduling/arbitration policies at the different resources (e.g., PEs and shared buses), our analysis can be used to compute upper bounds on the end-to-end delays associated with different event (and/or message) sequences. We illustrate the details of our analysis using a setup from the automotive electronics domain, where two real-life applications running on multiple electronic control units (ECUs) connected via a FlexRay bus. We show that compared to existing timing analysis techniques for distributed real-time systems, our proposed analysis gives tighter results, which immediately translate to better system design and improved resource dimensioning.

Organization of the Chapters: The rest of the thesis is organized as follows. The next two chapters discuss background and related work on system design models and timing analysis. In order to systematically obtain WCET estimation for individual tasks in a system specification, we propose a model-driven WCET analysis for tasks designed with Esterel specification in Chapter 4, 5, and 6. In particular, Chapter 4 considers the WCET estimation for a single Esterel clock tick execution, with automatical and lightweight infeasible path detection and elimination. We also discuss how to maintain and utilize a bi-directional traceability between Esterel model specification and the generated C programs for performance feedback and further WCET refinement. Chapter 5 shows how to incorporate program control flow and architecture contexts into timing analysis of task computation that spans multiple consecutive clock ticks. Chapter 5 extends the our timing analysis techniques to multiprocessor platforms. In Chapter 7,

we present our proposed system-level schedulability analysis for MSC-based globally asynchronous models. Finally, Chapter 8 presents the concluding remarks along with extensions and directions for future research.

# Chapter 2

# **Background**

## 2.1 Design Models

Synchronous models ([10]) provide a clear formalism for programming reactive systems, which exhibit high degree of concurrency but call for deterministic and predictable execution. Commonly used synchronous models in embedded system design include UML StateCharts [57], MATLAB Simmulink/Stateflow [101], and synchronous languages (Esterel [21], Lustre [54] and Signal [12]). Use of synchronous models simplifies the task of programming and makes such specifications amenable to formal verification/certification. Generating implementations directly from synchronous language specifications is widely practiced in safety-critical domains such as avionics where certification of the generated implementation is essential.

On the other hand, large-scale distributed computer systems are usually implemented by asynchronously composing several synchronous components, where each

component has its own clock. In such asynchronous model, reaction time of each local task and communication time between tasks are viewed by other tasks as finite and non-zero. It relaxes the behavior of the system, and allows the designer to refine one local task at a time.

In this work, we consider a fairly general system description with the Globally Asynchronous Locally Synchronous (GALS) model [25]. In particular, we adopt the synchronous language Esterel and asynchronous message sequence chart (MSC) to illustrate our model-driven timing analysis techniques.

#### 2.1.1 The Synchronous Language Esterel

Synchronous languages like Esterel have been widely adopted for designing reactive systems in safety-critical domains such as avionics and automobiles (e.g., [28]). Esterel is an imperative concurrent language. Specifications written in Esterel are based on the underlying "synchrony hypothesis", where all computation and communication, unless explicitly paused (using a pause statement), happen instantaneously. A run of a program typically consists of steps or *reactions* in response to *ticks* of a global clock. With each clock tick, a reaction computes the values of output *signals* and a new state from the input *signals* and the current state of the program. Such a reaction completes (in zero time) if it does not contain any pause, or else it delays the instructions following the pause until the next clock tick.

For example, the program "emit A; emit B; pause; emit C; pause; emit D" *emits* the signals A and B at the first tick, C at the second tick, and D at the

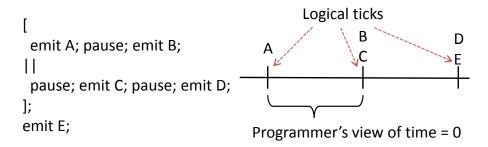

Figure 2.1: An example Esterel program

third tick. If p and q are Esterel statements, then p  $\|$  q is the parallel composition where p and q are executed concurrently with signals between p and q being transmitted instantaneously. Thus, the Esterel program shown in Figure 2.1 will emit signal A at the first tick, B and C at the second tick, followed by D and E in the third tick. Further details of the syntax and semantics of Esterel may be found in [21] (or from the references in [11]).

**Compiling Esterel.** Esterel programs can be compiled into C programs to be simulated/executed on general processor architectures. In principle, the generated C code should preserve the semantics of original Esterel program by

- implementing a *tick function*, such that one complete execution of the function (between its entry and exit) represents Esterel computation and communication required to be instantaneously executed within one clock tick. The tick function is loop-free, since Esterel allows no loops within a clock tick.

- encoding the automata of tick transitions within the tick function, which preserves

the context information of clock tick, and determines the path to be executed in

the tick function.

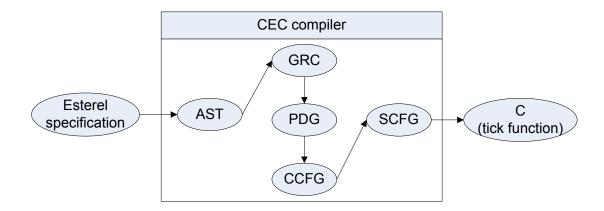

Figure 2.2: CEC compiler and the intermediate representations

• sequentializing the concurrent execution within a tick, based on the control dependencies (e.g., clock tick boundary, preemption) and communication dependencies (between set and test of signals) defined in the Esterel program.

Various techniques exist for compiling Esterel into sequential or distributed C programs ([90, 47]). Based on the intermediate representation used, they can be categorized into automata-based, netlist-based, and control flow graph-based approaches.

Automata based compiler (e.g., Berrys V3 [15]) exhaustively searches entire state space of the program and builds a product automata that captures all computation and communication in each clock tick. A separate branch is generated for each state in the automata (representing a possible clock tick). The generated code is very fast to run, with very small overhead to determine the state to be executed. However, size of tje generated code grows exponentially with number of concurrent threads in the specification.

Netlist based approaches (e.g., Berry's V4 and V5 [90]) translate each Esterel statement into a netlist of boolean logic gates. No statement duplication is required in the

generated code, which leads to much more compact code compared to the automata based compilation. However, the main drawback is the significant increase in execution time. This is due to all code in the source specification will get executed in each clock tick, even though some of them are not required to run [90].

In this work, we will focus our discussion on the control flow graph-based Esterel compilation, which normally produce fast and small C code. In particular, we have integrated our work into the control flow graph-based code generation of the Columbia Esterel Compiler (CEC) [34]. Figure 2.2 presents an overview of the CEC compiler and the intermediate representations used during Esterel-to-C compilation. CEC first parses an Esterel specification to build an abstract syntax tree (AST), which is then used to generate a variant of the so-called Graph Code (GRC) [90] through a syntax directed translation. GRC represents a concurrent structure of the desired cycle function and uses selection tree to encode the transition between cycles. It is an elegant way to represent the Esterel program, which allows optimizations to be performed prior to C code generation. The GRC is then transformed into a sequential control flow graph (SCFG), via a set of intermediate representations like program dependence graph (PDG), and concurrent control flow graph (CCFG). In CEC, these intermediate steps ensure that the concurrent control flow in GRC is sequentialized with the minimum number of context switches, while obeying the control/communication dependencies in original the Esterel program. Finally, sequential C code can be directly generated from the SCFG.

### 2.1.2 Message Sequence Charts

Message Sequence Charts (MSCs) or Sequence Diagrams are widely used by requirements engineers in the early stages of reactive system design [60, 93, 4]. MSCs can be very convenient for describing asynchronous interactions between a number of locally synchronous agents, e.g., a bus protocol between a bus controller and a number of processing elements trying to negotiate access to the bus. MSCs are therefore a natural choice for modeling and specifying distributed real-time and embedded systems.

**Definition 1** (Message Sequence Chart) An MSC is a labeled poset of the form  $Ch = (L, \{E_l\}_{l \in L}, \preceq, \lambda)$ , where

- L is the set of processes (also called lifelines) appearing in the chart as vertical lines.

- $E_l$  is the set of events that the lifeline l takes part in during the execution of Ch.

- $\preceq$  is the partial ordering relation over the occurrences of the events in  $\{E_l\}_{l\in L}$ .

The relation  $\preceq$  or  $\preceq^{Ch}$  (we put Ch as the superscript when necessary to highlight that the partial order belongs to chart Ch) is defined as follows.

- $\preceq_l^{Ch}$  is the linear ordering of events in  $E_l$ , which are ordered top-down along the lifeline l.  $\preceq_l^{Ch}$  is restricted to events on the same lifeline l, where  $\preceq_L^{Ch}$  is the collection of  $\preceq_l^{Ch}$  for all lifeline  $l \in L$ .

- $\preceq_{sm}^{Ch}$  is an ordering on message send/receive events in  $\{E_l\}_{l\in L}$ . If  $e_s$  is a send of message m by process p to process q, and the corresponding re-

ceive event is  $e_r$  (the receipt of the same message by process q), we have  $e_s \preceq_{sm}^{Ch} e_r$ . In rest of this thesis, we also refer the ordering on message send/receive events as communication dependency between the sender and receiver events.

-  $\preceq^{Ch}$  is the transitive closure of  $\preceq^{Ch}_L = \bigcup_{l \in L} \preceq_l$  and  $\preceq_{sm}$ , i.e.

$$\preceq^{Ch} = (\preceq_L^{Ch} \cup \preceq_{sm}^{Ch})^*$$

λ is the labeling function, with a suitable range of labels, which describes (a)

the messages exchanged by the lifelines and (b) the internal computational steps

during the execution of the chart Ch.

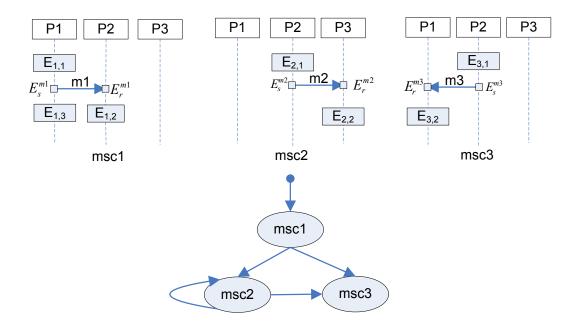

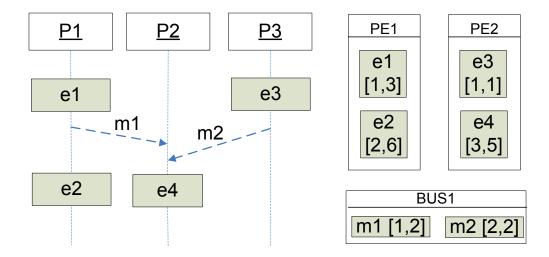

For example in the MSC msc1 in Figure 2.3, we have  $E_{1,1} \preceq_{P1}^{msc1} E_s^{m1} \preceq_{P1}^{msc1} E_{1,3}$  on the lifeline P1. For sending and receiving message m1 between P1 and P2, we have the ordering  $E_s^{m1} \preceq_{sm}^{msc1} E_r^{m1}$ . The transitive closure  $(\preceq_{P1}^{msc1} \cup \preceq_{P2}^{msc1} \cup \preceq_{sm}^{msc1})^*$  defines the following ordering

$$E_{1,1} \preceq_{P1}^{msc1} E_s^{m1} \preceq_{sm}^{msc1} E_r^{m1} \preceq_{P2}^{msc1} E_{1,2}$$

However, no ordering is imposed between  $E_{1,2}$  and  $E_{1,3}$  in msc1. Thus, an MSC defines a partial ordering relation over the events in the chart.

The preceding definition of MSC is an abstract one, and does not clarify the events appearing in an MSC. The complete MSC language ([60]) includes several types of events: message sends and receives, local actions, lost and found messages, instance creation and termination etc. However, for simplicity of exposition, we assume that

Figure 2.3: An example MSG

the events inside an MSC is of one of the following forms — *sends, receives and local events*. A local event can denote any terminating computation within a process, i.e., a terminating sequential program.

Each MSC in a system specification only denotes a *scenario* and captures the partial ordering between various computation and communication tasks/events constituting this scenario. Multiple such MSCs can be combined hierarchically to form high-level MSCs (HMSCs) [60], which involves choice, concatenation and iteration operations over a finite set of basic MSCs. HMSCs based specification is capable of capturing all possible system behaviors. In this work, we consider flattened HMSCs, which are known as message sequence graphs (MSGs) [3, 58], which describes the control flow (conditional execution) *between* MSCs.

**Definition 2** (Message Sequence Graph) An MSG can be defined as a directed graph  $MSG = (N, E, \circ)$ , where

- $N = \{MSC\} \cup \{\nabla\} \cup \{\triangle\}$  is the set of nodes in the MSG, where each node is either a basic MSC, or a special node  $\nabla$  ( $\triangle$ ) which denotes the unique initial (final) node respectively.

- E is the set of edges in the MSG, which represent the natural operation of chart concatenation between two nodes N<sub>1</sub> → N<sub>2</sub>. Two outgoing edges from a single node represent non-deterministic choice, so that exactly one of the two successor charts will be executed in an execution.

- o denotes the concatenation method between two nodes. We consider the socalled synchronous concatenation (not to be confused with synchronous models), where for a concatenation of two charts  $Ch \circ Ch'$  — all events in Ch' start only after chart Ch is finished.

Example of a simple MSG is shown in Figure 2.3. In the following we consider acyclic MSGs where there are no loops between initial state  $(\nabla)$  to the final state  $(\triangle)$ . An execution trace is defined to be a path from the initial state  $(\nabla)$  to the final state  $(\triangle)$  in the MSG and concatenates the sequence of MSCs encountered on the way. Of course, there is always an outer loop from final state  $(\triangle)$  to initial state  $(\nabla)$  denoting periodic behavior repeated forever. Our analysis can be extended to allow arbitrary loops in between the initial state  $(\nabla)$  to the final state  $(\triangle)$ , provided these (inner) loops are bounded.

## 2.2 Timing Analysis

Reliable timing analysis is of significant importance for safety-critical real-time system design, where the correctness of system depends on satisfaction of both functional and timing properties. To formally verify timing constraints, extensive studies have been proposed on static timing analysis methodologies. In this section, we provide an overview of two well-known categorizations of timing analysis approaches.

#### 2.2.1 WCET Analysis

Static worst-case execution time (WCET) analysis computes the maximum execution time of a program on a micro-architecture for all possible inputs. WCET analysis of a program involves finding the "longest" execution trace in the program's control flow graph (CFG). Recall that the nodes of a CFG are the basic blocks (maximal code fragments which are executed without control transfer), and the edges denote control transfer between basic blocks. Thus, a *path* in a control flow graph is simply a sequence of basic blocks, and an *execution trace* is a path executed for some program input. WCET analysis tries to find the maximum time the program takes to execute for any input.

Finding the weighted longest execution trace in a program can be done by running all possible inputs. However, this is not practical since (a) the number of inputs may be large, and (b) the program execution time for the same input may be different on different processors. WCET analysis methods typically solve this problem by developing a static analysis framework which takes as inputs (i) the program P being analyzed and (ii) a processor platform description Proc, and produces as output an overestimate of

Figure 2.4: Example C programs and control flow graphs.

the WCET of program P on processor Proc.

Static analysis based WCET estimation proceeds by finding the longest path in the program's control flow graph, satisfying certain loop bounds (e.g., in the example of Figure 2.4(a) the loop bound for the only loop is 10). The execution time estimate of each basic block is found by micro-architectural modeling where timing models of the processor micro-architecture (e.g., pipeline, cache, branch prediction) are developed to find the WCET of a sequence of instructions. Note that the WCET estimate of the instruction sequence corresponding to a basic block B is an upper bound on the execution time of B under all possible execution contexts.

With the knowledge of WCET of the basic blocks, finding the WCET of the whole program is reduced to an optimization problem. Here, we maximize the program execution time without enumerating the execution traces. This is done by expressing linear

constraints on the execution counts of any node/edge of the control flow graph. We then maximize an objective function representing the program execution time subject to these linear constraints. Since the execution counts of control flow graph nodes/edges are integers, we can employ Integer Linear Programming (ILP) technology. Formally, let  $\mathcal{B}$  be the set of basic blocks of a program. The program's WCET is given as:

maximize

$$\sum_{B \in \mathcal{B}} N_B * c_B$$

where  $N_B$  is an ILP variable denoting the execution count of basic block B and  $c_B$  is a constant denoting the WCET estimate of basic block B. The linear constraints on  $N_B$  are developed from the flow equations based on the control flow graph. Thus for basic block B,

$$\sum_{B'\to B} E_{B'\to B} = N_B = \sum_{B\to B''} E_{B\to B''}$$

where  $E_{B'\to B}$   $(E_{B\to B''})$  is an ILP variable denoting the number of times control flows through the control flow graph edge  $B'\to B$   $(B\to B'')$ . Additional linear constraints capture the loop-bounds (e.g., in Figure 2.4(a) we need to add the constraint  $E_{5\to 2} \le 10$ ).

Infeasible path detection. The core WCET estimation method outlined in the preceding is neither accurate nor automated. The cause of imprecision comes from the fact that many paths in the control flow graph might be *infeasible*, that is not appearing in the execution trace for any input. For example in the acyclic CFG shown in Figure 2.4(b), the execution path  $(B0 \to B2 \to B3 \to B4)$  cannot be taken for any program input, due to conflict between the assignment x = 0 (in B0) and the conditional branch

$B3 \rightarrow B4$  (which can be taken only if x! = 0). It is clearly that undue WCET overestimation is introduced if an infeasible path is considered to be the longest path in WCET analysis.

Many techniques have been proposed to detect and eliminate infeasible paths at source/assembly code level for WCET analysis ([78, 37, 104, 53]). In this work, we adopt a light-weight infeasible path detection technique based on the notion of conflicting pairs [104] — pairs of (assignment, branch) or (branch, branch) statements which may not appear together in an execution trace. Simply put, an assignment a on a variable x conflicts with a branch edge e (a branch edge refers to a branch condition being evaluated to either true or false) testing the same variable x if and only if (i) the test on x in e never succeeds with the value assigned in a, and (ii) there exists at least one path in the control flow graph between a and e which does not modify variable x. Similarly, a branch edge e1 testing a variable x conflicts with another branch edge e2 testing the same variable x if and only if (i) the conditions on x in e1 and e2 can never succeed together, and (ii) there exists at least one path in the control flow graph between e1 and e2 which does not modify variable x. Note that infeasible paths spanning across loop iterations are not captured by the definition of conflicting pair. Thus, [104] considers the control flow graph (CFG) to be a directed acyclic graph (DAG), representing the body of a loop. However, as we have discussed in Section 2.1.1, code generated from Esterel specification (the tick function) contains no loop within execution of a single clock tick. Thus, we do not detect infeasible paths spanning across loop iterations.

The notion of conflicting pair is extensively used in our model-driven timing anal-

ysis for synchronous model specification. To help readers have a better understanding the concept, we borrow the formal definition of conflicting pairs from [104].

**Definition 3** (Effect constraint) The effect constraint of an assignment var := expression is var == expression. The effect constraint of a branch-edge e in the CFG for a branch condition c is c ( $\neg c$ ) if e denotes that the branch is taken (not taken).

**Definition 4 (Conflicting pair)** A branch-edge (or assignment) x has (branch, branch) (or (assignment, branch)) conflict with a subsequent<sup>1</sup> branch-edge e if and only if

- Conjunction of the effect constraints of x and e is unsatisfiable, and

- There exists at least one path from x to e in the CFG that does not modify the variables appearing in their effect constraints.

In Figure 2.4(b), we list the (assignment, branch) and (branch, branch) conflicting pairs in the example acyclic CFG. Conflicting pairs capture only pairwise conflicts, which cannot detect (and exploit) arbitrary infeasible path information. However, we will show in this work that conflicting pair based infeasible path detection technique is efficient and effective for analyzing compiler generated code from high-level control-intensive models like Esterel.

### 2.2.2 Schedulability Analysis

Schedulability analysis decides for a given set of tasks under certain scheduling policy, whether all deadline requirement associated with each task can be satisfied. In order to

<sup>&</sup>lt;sup>1</sup>Subsequent in the sense of the topological order of the control flow DAG.

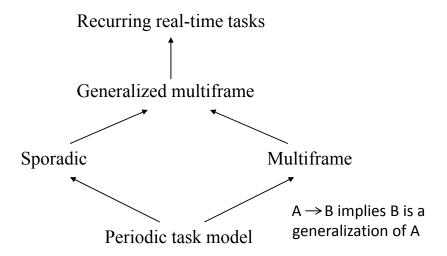

Figure 2.5: Relationship between the various task graph based models ([7]).

perform schedulability test for a set of tasks, one has to first characterize their (timing) behaviors into certain task models. The well-known periodic task model by Liu and Layland [74] makes following assumptions on each task in the task set.

- 1. Every task  $\tau_i$  is periodic, i.e. activated within a constant interval  $T_i$

- 2. Deadline of each instance of task  $\tau_i$  is the same and equal to its period  $T_i$

- 3. Each instance of task  $\tau_i$  has the same worst-case execution time  $C_i$

- 4. All tasks are independent, i.e. requests for a certain task do not depend on the initiation or the completion of requests for other tasks.

Based on periodic task model, many new task graph based models and corresponding schedulability analysis techniques have been proposed in recent works. In these models, one or more assumptions made in the periodic task model are relaxed, so that more complex system behaviors can be modeled. For example, the sporadic task model

[9] allows minimum separation time to be specified between two consecutive task releases, instead of the restricted constant period required in periodic task model. In multi-frame and generalized multi-frame task model ([82, 8]), execution time and deadline can be varied between different task instances (a.k.a. frames). Finally, recurring real-time task model [7] allows conditional execution between task instances. Figure 2.5 adopted from [7] summarizes relationship between the various task models.

When a set of tasks are running on shared resources, we need a scheduling policy to decide which task should be allowed to proceed when several of them are ready. Scheduling involves the allocation of resources to task in such a way that certain performance constraints are met. Different kinds of scheduling policies have been proposed ([91]), including the well-known Rate Monotonic scheduling (RMS) and Earliest Deadline First (EDF) scheduling.

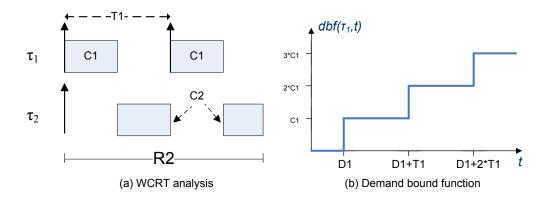

There are two standard categorizations of approaches for schedulability analysis of of real-time systems — worst-case response time analysis-based techniques (WCRT) [22, 55, 68], and the processor demand criteria-based analysis [8, 23].

WCRT analysis is used to test feasibility for a task set under static priority policy. The response time of a task is defined as the time interval between it releases and finishes execution. Response time of task  $\tau_i$  can be calculated by the following recursive equation

$$w_i^{n+1} = C_i + B_i + \sum_{j \in hp(i)} \lceil \frac{w_i^n}{T_j} \rceil \times C_j$$

where  $B_i$  is the blocking time of  $\tau_i$  by lower priority tasks(due to resource contention), and hp(i) contains the set of tasks whose priorities are higher than  $\tau_i$ . The recursive

Figure 2.6: Examples of Schedulability analysis approaches.

equation converges when  $w_i^{n+1} = w_i^n$  and this final value of  $w_i^n$  is the response time  $(R_i)$  of  $\tau_i$ . Then the feasibility test for a task set S is just to check that

$$\forall \tau_i \in S, R_i < D_i$$

where  $D_i$  is the explicit deadline of task  $\tau_i$ . Figure 2.6(a) shows an example of WCRT calculation. The worst case response time of  $\tau_2$  (labeled as R2 in the Figure) is equal to the summation of its worst case execution time C2 and  $2 \times C1$ , the time spent for execution of a higher priority task  $\tau_1$  within R2.

Another more general technique is called the processor demand criterion[23]. Processor demand criterion quantifies the maximum amount of processor time that all the jobs generated by the tasks can require in an interval of specified size, and attempts to determine whether there is an interval-size for which the processor demand criteria summed over all tasks in the system exceeds the processor capacity. Schedulability analysis using processor demand criterion will check that

$$\forall t \ge 0, t \ge \sum_{i=1}^{n} (\lfloor \frac{t - D_i}{T_i} \rfloor + 1) C_i$$

In other words, within any point of time t, the processor demand generated by all tasks in a task set must be smaller than or equal to the total available processing time (i.e., t). [23] shows that this checking only needs to be tested for a bounded value of t(the least common multiple LCM of all the task's period in the system). Figure 2.6(b) shows the processor demand of a task  $\tau_1$  over time t, given as the demand bound function  $dbf(\tau_1,t)$ . For example, no computation workload is required by  $\tau_1$  before its first deadline at time D1. While the processor must allocate C1 time unit to  $\tau_1$ , for the time period between [D1,D1+T1), i.e., before the deadline due for the second arrival of  $\tau_1$ . If a task set satisfies the processor demand criterion, there is an optimal uniprocessor scheduling algorithm(such as EDF) that manages to schedule it without missing any deadlines.

# Chapter 3

## **Related Work**

In this chapter, we present an overview of related work on timing analysis approaches for model based design framework.

## 3.1 WCET Analysis for Synchronous models

A real-life implementation generated from high-level synchronous models can be said to follow the synchrony hypothesis if all events that are logically assumed to be processed instantaneously are processed before the next set of events arrive. Verifying the synchrony hypothesis when a synchronous model is compiled into hardware is relatively straightforward. As a result, compiling synchronous language specifications directly into hardware is currently the most popular design flow ([14]).

On the other hand, when synchronous languages are compiled into software - e.g., into a sequential C code - validation of the synchrony hypothesis is more complicated

and depends on both the generated code, as well as the micro-architecture of the platform executing this code. For the synchrony hypothesis to hold, the estimated Worstcase Execution Time (WCET) associated with the processing of events should be less than the minimum separation time between the arrival of sets of events (that are assumed to be processed instantaneously).

#### 3.1.1 High-level WCET analysis

Architecture independent high-level timing analysis of Esterel (or Esterel-like) programs have been studied in [16, 100, 75]. Given a synchronous language specification, the task of a high-level WCET analysis is to compute the worst case computation time for a particular input event (or all allowed inputs), in terms of number of clock ticks required. This is usually done by translating the synchronous specification into a finite-state machine whose transitions correspond to clock ticks in the model ([98]). In other words, the *high-level* WCET analysis problem is concerned with the number of Esterel clock ticks, rather than the execution time of code within a clock tick. The timing analysis problem where the states of the automata have been annotated with WCET estimates has been discussed in [77]. Again, the focus here was not to obtain tight WCET estimates, but to analyze high-level timing properties of an Esterel specification, assuming that platform-level WCET estimates are already available.

[51] proposes an early stage WCET analysis to derive "approximate" WCET estimates at early stages of the software development process. Instead of performing executable code level WCET analysis on a target architecture, the early stage WCET analysis

ysis tries to construct a high-level timing model that contains approximate execution time information (i.e., a not guaranteed bound) on basic code constructs. Flow analysis is then performed on the timing model to find the worst case execution trace. Since the timing model can be built at any of the implementation levels between high-level model specification and executable code, early stage WCET analysis can be achieved. However, the analysis does not guarantee a safe upper bound on execution time, and its accuracy (how close to the real WCET) depends on many issues including (i) nature of the model specification (e.g., sequential or concurrent, imperative or declarative); (ii) model-to-executable compilation technique; (iii) and complexity of the target platform.

### 3.1.2 Code-level WCET analysis

Code-level WCET analysis for synchronous models aims to find architecture dependent execution time for computation within a single clock tick in the generated low-level executable code (e.g., C or assembly). [76] performs the low level WCET analysis for synchronous language Quartz (an Esterel-variation, see [98]) by building a formal transition model on the statements in the generated executable code. Transitions are labeled with the physical execution time of corresponding statements, and symbolic model checking is applied to search the "longest" WCET path. However, the presented technique is only applicable to automata-based code generation, which does not scale well for large Esterel programs.

The problem addressed in [94] is the closest to what we study in this work. Here, the problem of infeasible paths in the generated code is mentioned and timing anal-

ysis of the whole Esterel program is studied. Though the work can also be used for estimating the maximum computation in a clock tick, the methodology is restricted, since it requires two separate codes to be generated from the synchronous program — one on which the WCET analysis is performed, and one which guides the analysis. The approach in [94] is only feasible for the generation of circuit code, which tends to be slow for large-scale application specifications. Furthermore, the problem of bidirectional traceability or performance debugging of Esterel specifications — even though mentioned — was not studied on non-trivial Esterel benchmarks by including traceability links in an Esterel compiler.

Code-level WCET analysis techniques for other synchronous models, e.g., State-Charts [57] and MATLAB Simulink [101], have been also studied ([38, 65]). Recent advances in WCET analysis techniques and the availability of industry-strength tools ([42, 109]) has renewed the interest in synchronous language-based design flows targeting general-purpose platforms. A WCET analysis framework that integrates the synchronous language SCADE [97] from Esterel Technologies with the aiT WCET analyzer from AbsInt GmbH [1], targeting general-purpose processors, was presented in [59]. In [59], the WCET analysis is ignorant to the fact that the executable code is compiled from a high-level modeling language. On the other hand, our proposed model-driven timing analysis framework (discussed in Chapter 4, 5, and 6) automatically utilizes model-level information in low-level WCET analysis, which leads to more efficient and tighter WCET estimation. Very recently, [105] proposes a technique to improve timing analysis for MATLAB Simulink/Stateflow model, by incor-

porating model-level flow information into WCET analysis. However, the model-level flow constraints are manually identified and translated into code-level flow constraints for WCET calculation.

#### 3.1.3 Timing analysis for special-purpose architecture

Special-purpose reactive processors have been developed to support concurrent execution of Esterel specification, where instead of compiling into C code, the Esterel specification is mapped to a concurrent reactive processing ISA. Example architectures include EMPEROR [111], STARPro [112] and Kiel Esterel processor (KEP) [69, 71].

Timing analysis for execution of Esterel specifications on the special-purpose reactive processors have been studied in [69, 111, 19, 81]. Recently, similar approaches have also been followed for timing analysis of a synchronous version of C, called PRET-C, to be implemented on special precision timed or PRET architectures [95]. Compared to timing analysis of general-purpose processors, micro-architectural modeling for such special-purpose processors is simplified to a large extent. Furthermore, special-purpose reactive processors implement hardware supports for handling concurrency and other Esterel semantics (e.g., preemption and event broadcasting). As a result, timing analysis designed for these architectures can not be applied to the general-purpose processor setting. In this work, we focus on timing analysis of Esterel specifications on general-purpose processor architectures.

## 3.2 Schedulability Analysis for Distributed System

Tindell et al. [107] propose a holistic schedulability analysis for distributed real-time systems, which bounds the worst case delays of both local computations and interprocessor communications. However, their analysis assumes only a simple static TDMA protocol for the bus communication, and the communication dependencies are not taken into consideration (thereby leading to coarse analysis and pessimistic results). In [89], timing analysis for distributed system connected via a shared FlexRay bus ([44]) is presented. The analysis focuses on bounding the messages transmission time in both the static and the dynamic segments of a FlexRay communication cycle. The discussed schedulability analysis is applicable to task models with only communication dependencies, where conditional execution of task is not supported. Recently, schedulability test has been proposed for *independent* sporadic tasks executed on uniform multiprocessors with global EDF scheduler.

Although the task graph based models introduced in Section 2.2.2 naturally represent periodically or sporadically executing applications [35, 86], they only provide *local* or *processor-centric* views of a distributed system. More specifically, the structuring mechanism used revolves around specifying all the tasks that execute on any given processing (or communication) element. As a result, they are not very suitable for specifying the *interactions* between the multiple entities of a distributed system – which is often a more natural way of specifying such systems.

There are two standard approaches for schedulability analysis of task graph-based specifications of real-time systems — worst-case response time analysis-based tech-

niques [22, 55, 68], and the processor demand bound criteria-based analysis [8, 23] (refer to Section 2.2.2 for a brief discussion). Recently, the response time analysis has been extended for schedulability analysis of periodic/sporadic task sets (of independent tasks) on multiprocessor platform [17, 50]. However, it turns out that neither of these approaches can be applied to our setting in a straightforward manner. This is primarily because in traditional task graph-based specifications, all the vertices are mapped onto a single resource, whereas in our case each globally asynchronous MSG (in fact even a vertex of an MSG denoting an MSC) involves multiple computation and communication resources. Hence, the semantics of MSGs are fundamentally different from the task graph based models that have been studied in the real-time systems literature.

Our proposed schedulability analysis for MSC-based system model is motivated by the response time calculation algorithm presented in [110], which can handle system specifications with multiple computation and communication elements. We have adapted this algorithm to the specific context of MSCs, and in particular proposed two new extensions.

• The algorithm in [110] is based on a response time analysis framework, which iteratively computes tighter estimates on the response times of various computation and communication tasks. However, it cannot handle conditional or non-deterministic branches which exist in MSGs. We get around this problem by combining the response time analysis-based technique in [110] with a demand bound criteria-based technique that was proposed in [7] to handle conditional branches in a different task model.

• Compared to [110], we also obtain tighter bounds on the response times of tasks by accounting for the dependencies in the preempting tasks/applications, by calculating request bound from higher priority tasks during the response time of the preempted task (event).

The main novelty of our work stems from the combination of response time analysis and demand bound criteria-based techniques, which is not commonly seen in the real-time systems literature.

Finally, we would like to point out that there have been a few previous attempts towards developing schedulability analysis techniques for MSC-based system models [96, 102]. However, they either do not fully exploit the communication dependencies within an MSC, or are restricted to the analysis of a single MSC (as opposed to a complete system model).

# **Chapter 4**

# **Performance Debugging of Esterel**

In this chapter, we propose a timing analysis technique for WCET estimation of a single Esterel tick. Such estimates can validate Esterel-level assumptions on the instantaneous processing of signals or events that occur together (Section 2.1.1). More importantly, with our automatically built traceability between Esterel specification and generated C code, they can be used to identify parts of the specification which might pose as timing/performance bottlenecks with respect to the underlying platform. We show the results of our WCET analysis on a set of standard Esterel benchmarks and illustrate the utility of our model-to-code traceability technique using an Esterel specification of a reflex game application.

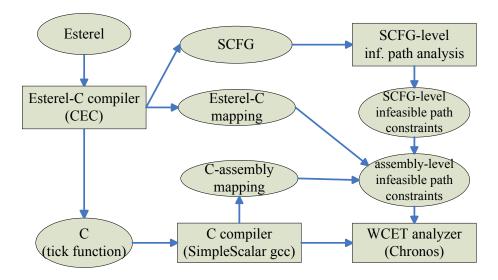

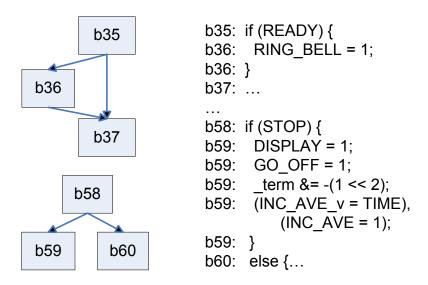

Figure 4.1: WCET analysis of a single Esterel tick.

#### 4.1 Overview

Figure 4.1 gives an overview of our WCET analysis framework. We use the Columbia Esterel Compiler [34]) to compile a given Esterel program into C, and calculate the WCET of the C code via a ILP-based platform-aware WCET analyzer. The generated C program is in the form of tick function (refer to Section 2.1.1), where one complete execution of the tick function (between its entry and exit) represents all computation and communication required to be processed instantaneously within one clock tick. As a result, we can validate that the synchrony hypothesis assumed at model level indeed holds in the real implementation, if the WCET of generated tick function is guaranteed to be less than the minimum separation time between the arrival of sets of input events.

For C code generated from Esterel specifications, the user can largely avoid the problems related to automation of the WCET analysis (refer to Section 2.2.1). In particular, since the tick function is loop-free (Esterel allows no loops within a clock tick),

this leads to an acyclic control flow graph and hence there is no need to provide loop bounds to the WCET analyzer. Since each basic block is executed at most once in one execution of the tick function, and ILP-based WCET analysis produces a 0-1 assignment for the execution count of each basic block. However, compiler generated programs, especially from high-level control-intensive specifications, usually contain huge number of infeasible execution paths compared to hand-written code. As a result, WCET overestimation due to infeasible execution paths is largely amplified in timing analysis of compiler generated programs.

We propose a comprehensive and light-weight infeasible path detection and elimination technique for WCET estimation of programs generated from Esterel specification. Our proposed infeasible path detection is performed at sequential control-flow graph (SCFG) level, which is a standard intermediate representation used in control-flow graph-based Esterel compilation. The computed SCFG-level infeasible path constraints are translated into assembly-level infeasible path constraints, via our Esterel-C mapping (obtained by instrumenting the CEC compiler) and the C-assembly mapping (obtained by disassembling the compiled C code). Finally, we integrate the assembly-level infeasible path constraints into the ILP formulation generated by Chronos ([41]), an ILP-based WCET analyzer. WCET value and corresponding critical path for a single tick execution of the Esterel specification on a specific platform can be obtained by solving the resulted ILP formulation. In summary, we use the pattern of the generated code to identify infeasible path patterns, which are then taken into account during the timing analysis.

#### 4.2 Infeasible Path Patterns

We observe that the automatically generated C code (from Esterel) often contains certain infeasible path patterns which may be less frequent in hand-written C code. Thus, low-overhead automatic methods for detecting/exploiting infeasible path information can substantially reduce the WCET of such automatically generated C code. Based on our study of C programs generated via Esterel compilation to sequential control flow graphs, we found the following four common sources of infeasible paths. For each of these four sources, in Figure 4.2 we show example Esterel program fragments and the corresponding C code (labeled with line numbers) generated by the default code generation mechanism in the Columbia Esterel Compiler [34]. We adopt the notion of conflicting pairs which has been presented in Section 2.2.1 in our discussion of infeasible path patterns. The four infeasible path pattern categorizations are as follows.

Emit and test signals. The corresponding infeasible paths are also presented at the C level, e.g., the conflicts due to assignment and test on signal A (L1 and L2 → L4) in the first program fragment shown in Figure 4.2. Besides, in an Esterel clock tick, the same signal may be tested in different concurrent threads. As a result, in the generated C program, multiple identical tests on the same signal variable will result in paths with (branch, branch) conflicts (refer to Section 2.2.1). For example, the two conditional tests on signal A at L2 and L5 in the first program fragment in Figure 4.2 introduce two conflicting pairs, (L2 → L3, L5 → L7) and (L2 → L4, L5 → L6).

| Type 1       | Generated C code           | Type 2       | Generated C code                          |  |  |

|--------------|----------------------------|--------------|-------------------------------------------|--|--|

| emit A;      | L1: <b>A = 1</b> ;         | emit A;      | L1: A = 1;                                |  |  |

| present A    | L2: if (A)                 | present B    | L2: _DPSCUT_VAR2 = 0;                     |  |  |

| then emit B  | L3: B = 1;                 | then         | L3: $\overline{if}(A) B = \overline{1}$ ; |  |  |

| else emit C; | else                       | end present  | L4: else D = 1;                           |  |  |

| end present  | L4: C = 1;                 | l II         | L5: if (_DPSCUT_VAR2) {                   |  |  |

|              | L5: <b>if (A)</b>          | present A    | L6:                                       |  |  |

| present A    | L6: D = 1;                 | then         | } else {                                  |  |  |

| then emit D; | else                       | emit B;      | L7: if (B) {}                             |  |  |

| else emit E; | L7: E = 1;                 | else emit D; | }                                         |  |  |

| end present  |                            | end present  |                                           |  |  |

| Type 3       | Generated C code           | Type 4       | Generated C code                          |  |  |

| trap T in    | /*exit T */                | loop         | L1: if (_state_3) {                       |  |  |

| [            | L1: _term_17 &= -(1 << 2); | emit A0;     | L2: A0 = 1; _state_3 = 0;                 |  |  |

| exit T;      | L2: B = 1;                 | pause;       | } else {                                  |  |  |

| pause;       | /*pause */                 | emit A1;     | L3: A1 = 1; _state_3 = 1;                 |  |  |

|              | L3: _term_17 &= -(1 << 1); | pause;       | }                                         |  |  |

|              |                            | l II         | L4: if (_state_6) {                       |  |  |

| emit B;      | L4: switch (~_term_17) {   | emit B0;     | L5: B0 = 1; <b>_state_6 = 0</b> ;         |  |  |

| pause;       | L5: case 0: break;         | pause;       | } else {                                  |  |  |

|              | L6: case 1: break;         | emit B1;     | L6: B1 = 1; <b>_state_6 = 1</b> ;         |  |  |

| ]            | //pause                    | pause;       | }                                         |  |  |

| emit C       | L7: case 3:                | end          |                                           |  |  |

|              | L8: C = 1; break; //exit   |              |                                           |  |  |

|              | T                          |              |                                           |  |  |

Figure 4.2: Example infeasible path patterns in generated C code.

2. Sequentialization of concurrency in a tick. To generate sequential C code from a concurrent Esterel program, communication dependencies (between emit and test of a signal) and context switches between concurrent threads must be captured. In CEC, this is handled by inserting new control variables and corresponding test nodes in the generated C code, when the concurrent control flow graph CCFG is translated into sequential control flow graph SCFG (refer to Figure 2.2). In the second program fragment (Figure 4.2), the variable \_DPSCUT\_VAR2 captures the state of the first thread before a context switch (by setting its value to 0 at L2), and is used as a conditional guard when the thread resumes execution at L5. Such assignments and tests (may be at multiple places in the same clock tick) on the guard will introduce possible infeasible paths. In our example code fragment, the

(assignment, branch) conflicts (refer to Section 2.2.1) between L2 and  $L5 \rightarrow L7$  introduces infeasible paths in the generated C code.

- 3. Termination and preemption. The multi-threaded Esterel program follows the "wait for all threads to terminate" and "winner takes all" behaviors for thread completion and thrown exceptions ([34]). In the C code generated from CEC, this is handled by setting and testing the values of newly introduced guard variables (e.g. variable \_term\_17 as in the third example in Figure 4.2). These guard variables are assigned to non-negative integer values during the execution of each thread (0 for thread terminating, 1 for pausing, 2 and higher for throwing and exception). Such assignments and the tests on these guard variables (e.g., (L1, L4 → L6) on value of \_term\_17) introduce possible infeasible paths.

- 4. Encoding tick transitions. In Esterel, a global automata is defined on the sequence of ticks to be executed in each thread, via the use of "pause" and "await" statements. In the generated C code, this automata is encoded through a set of state variables. Setting and testing these state variables introduce infeasible paths since certain combinations of states are not allowed in the automata. For example, in the last program fragment, given the initial value [0,0], the combinations of values of ([\_state\_3, \_state\_6]) can only be [0,0] or [1,1] which prevents the paths corresponding to evaluation of [\_state\_3, \_state\_6] to be [0,1] or [1,0]. In particular, the path contains branches L1 → L2 and L4 → L6 cannot appear in any feasible execution trace of the program.

#### 4.3 SCFG-level Infeasible Path Detection