# NATIONAL UNIVERSITY OF SINGAPORE

# CS2100 – COMPUTER ORGANISATION

(Semester 2: AY2024/25)

Time Allowed: 2 Hours

# **INSTRUCTIONS TO STUDENTS**

- 1. This assessment paper consists of **TWENTY THREE (23)** questions in **TWO (2)** parts and comprises of **FIFTEEN (15)** printed pages.

- 2. Answer ALL questions on the **ANSWER SHEETS**.

- 3. This is an **OPEN BOOK** assessment.

- 4. Write your answers only on the **ANSWER SHEETS**. You may write in pen or pencil. You are to write within the space provided. No extra pages should be submitted.

- 5. Printed/written materials are allowed. Apart from calculators, electronic devices are not allowed.

- 6. Page 15 contains the MIPS Data Reference sheet.

- 7. The maximum mark of this assessment is 100.

| Question      | Max. mark |

|---------------|-----------|

| MCQs: Q1 – 18 | 36        |

| Q19           | 12        |

| Q20           | 14        |

| Q21           | 13        |

| Q22           | 12        |

| Q23           | 13        |

| Total         | 100       |

---- END OF INSTRUCTIONS ----

### Part A: Multiple-Choice Questions [Total: 18×2=36 marks]

Each multiple-choice question (MCQ) is worth **TWO marks** and has exactly **one** correct answer. Please shade the corresponding bubbles on the Answer Sheets.

1. What is the output of the following C program?

```

#include <stdio.h>

struct Item {

int x;

int y;

};

void foo(struct Item *item, int n) {

for (int i = 0; i < n; i++) {

if ((item + i)->x % 2 == 0)

continue;

if ((item + i) ->y + (item + i) ->x > 12)

break;

(item + i) ->y += (item + i) ->x;

}

}

int main() {

struct Item item[4] = {{1, 4}, {2, 6}, {3, 7}, {5, 2}};

foo(item, 4);

for (int i = 0; i < 4; i++)

printf("%d ", item[i].y);

return 0;

}

```

A. 5 6 10 7

B. 5 6 7 2

C. 4 6 10 7

D. 5 6 10 2

E. None of options (A), (B), (C), (D) are correct.

2. What is the output of the following C program?

```

#include <stdio.h>

int foo(int *x) {

return (*x)++;

}

int main() {

int a = -1, b = 2, c = -1, result = 0;

if ((a || foo(&b)) && (foo(&c) && !c)) {

result = a + b + c;

}

printf("b = %d, c = %d, result = %d\n", b, c, result);

return 0;

}

A. b = 3, c = 0, result = 2

```

B. b = 2, c = 0, result = 0 C. b = 2, c = 1, result = 0 D. b = 2, c = 0, result = 1 E. None of options (A), (B), (C), (D) are correct.

- 3. An 8-bit register contains the value 3333 in base-4. A student assumes this is a large positive number. However, the register uses 2's complement format to represent signed integers. What is the correct signed decimal value of this 8-bit 2's complement number?

- A. 255

- В. –1

- С. –127

- D. 0

- E. None of options (A), (B), (C), (D) are correct.

- 4. The 32-bit IEEE 754 hexadecimal floating-point number **0x3F838000** corresponds to which of the following decimal values?

- A. 1.015625

- B. 1.02734375

- C. 1.03125

- D. 1.0625

- E. None of options (A), (B), (C), (D) are correct.

- 5. You are given the following 32-bit MIPS-x instruction in hexadecimal: **0x212A000A**.

In this MIPS-x system, everything is identical to the MIPS system, except the immediate field which uses excess-2<sup>15</sup> encoding. Which of the following is the correct decoded MIPS-x assembly instruction?

- A. addi \$t1, \$t2, 10

- B. addi \$t2, \$t1, 10

- C. addi \$t1, \$t2, -32758

- D. addi \$t2, \$t1, -32758

- E. None of options (A), (B), (C), (D) are correct.

- 6. A MIPS processor has a fault in one control signal, causing the following behaviour:

- addi and lw instructions do not work correctly

- R-type instructions (e.g., add) work correctly

- sw instruction works correctly

- Which control signal is most likely stuck at the wrong value?

- A. MemtoReg stuck at 1.

- B. RegDst stuck at 1.

- C. ALUSrc stuck at 0.

- D. MemRead stuck at 1.

- E. None of options (A), (B), (C), (D) are correct.

- 7. Which of the following Boolean laws/theorems is/are used to simplify  $P \cdot Q' + Q' \cdot R' + P' \cdot R'$ into  $P \cdot Q' + P' \cdot R'$ ?

- A. Distributive law

- B. Absorption theorem 1 and DeMorgan's theorem

- C. Complement law and idempotency theorem

- D. Consensus theorem

- E. None of options (A), (B), (C), (D) are correct.

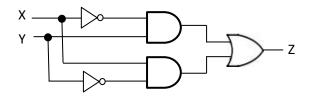

- 8. Name the logic gate that is equivalent to the circuit below.

- A. NAND gate

- B. NOR gate

- C. XOR gate

- D. XNOR gate

- E. None of options (A), (B), (C), (D) are correct.

- 9. What is the minimum number of 2-input NAND gates required to implement an XOR gate?

- A. 3

- B. 4

- C. 5

- D. 6

- E. None of options (A), (B), (C), (D) are correct.

- 10. How many <u>unique minterms</u> does the following 5-variable Boolean function contain?

$$F(A,B,C,D,E) = C' \cdot E' + C \cdot D \cdot E + B \cdot C' \cdot D + A \cdot B \cdot D$$

- A. 12

- B. 15

- C. 18

- D. 20

- E. None of options (A), (B), (C), (D) are correct.

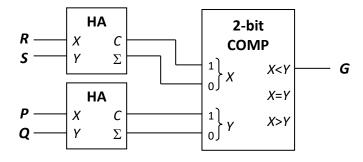

11. Given the following circuit using a 2-bit magnitude comparator and two half adders (HA), what is the function G(P, Q, R, S)? (*C* and  $\Sigma$  are the carry and sum outputs of the half adder respectively.)

- A.  $\Sigma m(1, 2, 3, 6, 7, 11)$

- B. Σ*m*(4, 8, 9, 12, 13, 14)

- C. Σm(1, 2, 3, 7, 11)

- D. Σ*m*(4, 8, 12, 13, 14)

- E. None of options (A), (B), (C), (D) are correct.

- 12. Which of the following statements are true?

- (i) Every maxterm is a product term.

- (ii) A literal is both an SOP expression and a POS expression.

- (iii) Every Boolean expression can be rewritten into POS form.

- A. Only (i) and (ii).

- B. Only (i) and (iii).

- C. Only (ii) and (iii).

- D. All of (i), (ii) and (iii).

- E. None of options (A), (B), (C), (D) are correct.

- 13. Given the Boolean function:  $Z(A,B,C,D) = \Sigma m(1,2,3,9,11,12,15) + \Sigma x(4,5,6,7,13,14)$

where x's are don't-cares, and an 8-to-1 multiplexer with selector lines  $S_2$  (most significant),  $S_1$  and  $S_0$ . Assuming that logical constants are available but not complemented literals, which of the following settings <u>cannot</u> implement the function Z if no additional logic gates are allowed?

- A.  $S_2S_1S_0 = ABC$

- $\mathsf{B}. \quad S_2 S_1 S_0 = ABD$

- $C. \quad S_2 S_1 S_0 = BCD$

- $\mathsf{D}. \quad S_2 S_1 S_0 = CBA$

- E. None of options (A), (B), (C), (D) are correct.

- 14. Given the Boolean function  $F(A,B,C,D) = \Sigma m(0,3,6,9,11) + \Sigma x(2,4,5,7,13,15)$  where x denotes don't-care, how many prime implicants are there in the K-map of F?

- A. 3

- B. 4

- C. 5

- D. 6

- E. None of options (A), (B), (C), (D) are correct.

- 15. Given the Boolean function F(A,B,C,D) = Σm(0,3,6,9,11) + Σx(2,4,5,7,13,15) where x denotes don't-care (same as the question above), how many essential prime implicants are there in the K-map of F?

- A. 3

- B. 4

- C. 5

- D. 6

- E. None of options (A), (B), (C), (D) are correct.

- 16. The 4221 code and 8421 code (or BCD code) introduced in the tutorial are two examples of decimal codes. Self-complementing decimal codes are codes such that given any decimal digits *x* and *y* which are 9's complements of each other, their corresponding codes are 1's complement of each other. (For example, 0010 and 1101 are the 4221 codes of decimal digits 2 and 7 respectively. The 4221 code is self-complementing but 8421 code is not.

(Note that there are alternative 4221 codes for decimal digit 2, such as 0010 and 0100. As long as there is a way such that any two complementary decimal digits have their corresponding codes that are complementary in binary, it is considered a self-complementing code.)

Which of the following codes are self-complementing?

- (i) 84-2-1 code (the weights are 8, 4, -2 and -1)

- (ii) 5211 code

- (iii) 4321 code

- A. Only (i).

- B. Only (ii).

- C. Only (i) and (ii).

- D. Only (ii) and (iii).

- E. None of options (A), (B), (C), (D) are correct.

17. Which of the following symbols is used for logic gate inputs in Logisim?

- D. 🍼

- E. None of options (A), (B), (C), (D) are correct.

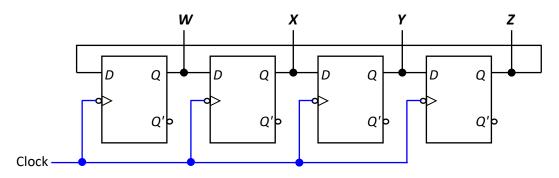

- 18. The sequential circuit below is implemented using D flip-flops.

Suppose the circuit is initialised with the value *WXYZ* = 0101, how many unique states does the circuit cycle through?

- A. 2

- B. 4

- C. 8

- D. 16

- E. None of options (A), (B), (C), (D) are correct.

# Part B: There are 5 questions in this part [Total: 64 marks]

### Q19. Sequential circuit [12 marks]

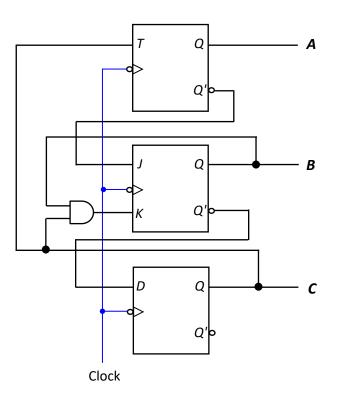

A sequential circuit with states ABC is implemented using a T flip-flop, a JK flip-flop and a D flip-flop as shown below.

- (a) Complete the state diagram on the Answer Sheets. Two of the transition arrows have been drawn for you.

- (b) List out all the sink states in <u>decimal values</u> (that is, if *ABC*=101 is a sink state, write the value 5 instead of 101). If there are no sink states, write "none" instead of leaving a blank answer. [1]

- (c) Redesign the circuit using only *T* flip-flops. Write out the flip-flop input functions *TB* and *TC* in the simplest SOP expressions.

[4]

- (d) Assuming that part (c) is correctly answered, if *TB* and *TC* are to be implemented using the fewest number of logic gates, at least how many logic gates in total are required to implement *TB* and *TC*? Logic gates available are inverters, AND, OR, NAND, NOR, XOR and XNOR gates.

### Q20. Combinational circuits [14 marks]

Note that logical constants 0 and 1 are available, but not complemented literals.

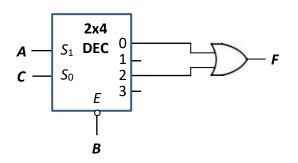

(a) Given a 0-enable active-high output 2×4 decoder as shown below, what is the simplified SOP expression for F ?

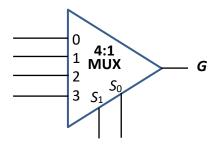

(b) Let  $G(A,B,C,D) = \prod M(1,3,4,12)$ . Implement G using a single 4:1 multiplexer without any additional logic gate. Complete the diagram on the Answer Sheets. [4]

(c) In class, we have discussed the design of the ALU Control Unit for the following set of instructions: lw, sw, beq, add, sub, and, or, slt. Suppose the funct values of all R-format instructions are changed. The new funct values (in base 10) for the 5 R-format instructions are given below:

| R-format instruction   | add | sub | and | or | slt |

|------------------------|-----|-----|-----|----|-----|

| funct value in base 10 | 27  | 19  | 11  | 43 | 51  |

Write out the simplified SOP expressions for ALUcontrol2, ALUcontrol1 and ALUcontrol0.

(Use ALUop1 and ALUop0 for the 2-bit ALUop, with ALUop1 being the MSB. Use F5, F4, F3, F2, F1 and F0 for the 6-bit funct field, with F5 being the MSB and F0 the LSB.) [6]

#### Q21. MIPS [13 marks]

Study the following MIPS code on integer arrays *A* and *B*, with both arrays having the same number of elements. The variable mappings are given below:

- \$a0 = size (number of elements in array A)

- \$a1 = base address of array A

- \$a2 = base address of array B

```

.data

size: .word 9

A: .word 23, 13, 16, 20, 100, 17, 82, 12, 80 # contents of array A

B: .word 11, 22, 33, 44, 55, 66, 77, 88,99

# contents of array B

.text

main: la

$t0, size

# $t0 is the address of size

# $a0 is the content of size

lw

$a0, 0($t0)

$a1, A

# $a1 is the base address of array A

la

$a2, B

# $a2 is the base address of array B

la

------

add $t0, $0, $0

# Inst1

addi $t1, $a1, 0

# Inst2

addi $t2, $a2, 0

# Inst3

loop: slt

$t9, $t0, $a0

# Inst4

$t9, $0, exit # Inst5

beq

$s1, 0($t1)

# Inst6

lw

$s2, 0($t2)

# Inst7

lw

andi $s3, $s1, 3

# Inst8

$s3, $0, skip # Inst9

bne

# Inst10

addi $s2, $s2, -1

sw

$s2, 0($t2)

# Inst11

skip: addi $t0, $t0, 2

# Inst12

addi $t1, $t1, 8

# Inst13

addi $t2, $t2, 8

# Inst14

loop

# Inst15

j

# ____

exit: li

$v0, 10

# system call code for exit

syscall

```

(a) Write out the contents of array *B* after the execution of the above MIPS code.

[2]

[3]

- (b) Using the variable names (*size*, *A*, *B*) given in the variable mappings, write an equivalent C code that corresponds to instructions Inst1 to Inst15, using a 'for' loop. You may use additional variable(s) if necessary. You do not need to declare the variables in your C code. Do <u>not</u> do a line-by-line direct translation of the MIPS code. Marks may be deducted if your code is convoluted or unnecessarily long.

- (c) With the given contents of arrays A and B, and considering only instructions Inst1 to Inst15, how many instructions are executed in total by the code?[2]

- (d) Write the encoding of Inst6 (lw \$s1, 0(\$t1)) in hexadecimal. [2]

- (e) Write the encoding of Inst9 (bne \$s3, \$0, skip) in hexadecimal. [2]

- (f) Assuming that Inst15 (j loop) is stored at address **0x0020 0000**, write the encoding of Inst15 (j loop) in hexadecimal. [2]

### Q22. Pipelining [12 marks]

Study the MIPS code below, which is the same code in Q21, with only Inst1 to Inst15 shown. The variable mappings are given below:

- \$a0 = size (number of elements in array A)

- \$a1 = base address of array A

- \$a2 = base address of array B

|       | add  | \$t0, | \$O, \$O   | # | Inst1  |

|-------|------|-------|------------|---|--------|

|       | addi | \$t1, | \$a1, 0    | # | Inst2  |

|       | addi | \$t2, | \$a2, 0    | # | Inst3  |

| loop: | slt  | \$t9, | \$t0, \$a0 | # | Inst4  |

|       | beq  | \$t9, | \$0, exit  | # | Inst5  |

|       | lw   | \$s1, | 0(\$t1)    | # | Inst6  |

|       | lw   | \$s2, | 0(\$t2)    | # | Inst7  |

|       | andi | \$s3, | \$s1, 3    | # | Inst8  |

|       | bne  | \$s3, | \$0, skip  | # | Inst9  |

|       | addi | \$s2, | \$s2, -1   | # | Inst10 |

|       | sw   | \$s2, | 0(\$t2)    | # | Inst11 |

| skip: | addi | \$t0, | \$t0, 2    | # | Inst12 |

|       | addi | \$t1, | \$t1, 8    | # | Inst13 |

|       | addi | \$t2, | \$t2, 8    | # | Inst14 |

|       | j    | loop  |            | # | Inst15 |

| exit: |      |       |            |   |        |

|       |      |       |            |   |        |

Assuming a 5-stage MIPS pipeline, you need to count until the last stage (WB stage) of Inst15. Assume that no delayed branching is used and the jump instruction (j) computes the target address to jump to in its ID stage (stage 2). Assume that the contents of arrays A and B are the same as in Q21; in particular, A[0] = 23.

(a) How many cycles does the code segment Inst1 to Inst15 take to complete its execution in the first iteration in an ideal pipeline, that is, one with no delays? [1 mark]

For parts (b) to (d) below, given the assumption for each part, how many <u>additional cycles</u> does the code segment Inst1 to Inst15 take to complete its execution in the first iteration as compared to an ideal pipeline computed in (a)? For example, if part (a) takes 30 cycles and part (b) takes 39 cycles, you should write **9** as the answer for part (b).

| (b) | Assuming without forwarding and branch decision is made at MEM stage (stage 4). |           |

|-----|---------------------------------------------------------------------------------|-----------|

|     | No branch prediction is made.                                                   | [3 marks] |

| (c) | Assuming with forwarding and branch decision is made at MEM stage (stage 4).    |           |

|     | No branch prediction is made.                                                   | [3 marks] |

| (d) | Assuming with forwarding and branch decision is made at ID stage (stage 2).     |           |

|     | Branch is predicted not taken.                                                  | [3 marks] |

(e) Assume the configuration in part (b). Let's call the given code X. Suppose we swap Inst7 and Inst8 and call the new code Y. Would X be better than Y (X takes fewer cycles than Y to complete), or would X be worse than Y (X takes more cycles than Y to complete), or the same (X and Y take the same number of cycles to complete)? Write "Better", "Worse" or "Same" on the Answer Sheets.

[2 marks]

### Q23. Cache [13 marks]

Study the MIPS code below, which is the same code in Q21, with only Inst1 to Inst15 shown. The variable mappings are given below:

- \$a0 = size (number of elements in array A)

- \$a1 = base address of array A

- \$a2 = base address of array B

| Ħ | Inst1  |

|---|--------|

| # | Inst2  |

| # | Inst3  |

| # | Inst4  |

| # | Inst5  |

| # | Inst6  |

| # | Inst7  |

| # | Inst8  |

| # | Inst9  |

| # | Inst10 |

| # | Inst11 |

| # | Inst12 |

| # | Inst13 |

| # | Inst14 |

| # | Inst15 |

|   |        |

|   | ***    |

In this question, we consider only memory read accesses (lw) and ignore memory write accesses (sw).

You are to assume that array B follows immediately after array A in the memory, that is, if the last element of array A is at address x, then B[0] is at address x + 4.

Parts (a) to (e) are on **data cache** with **each block containing 8 words**.

- (a) How many bits are there in the byte offset field?

- (b) Given a direct-mapped data cache with a capacity of 512 words, how many bits are there in the index field? [1 mark]

- (c) Given a direct-mapped data cache with a capacity of 512 words, arrays A has **1028** elements, array B has the same number of elements, and the base address of array A is at 0x10010004, how many memory read access cache hits in total are there?

[3 marks]

- (d) Given a 2-way set-associative data cache with a capacity of 512 words, how many bits are there in the set index field? [1 mark]

- (e) Given a 2-way set-associative data cache with a capacity of 512 words, arrays A has **1028** elements, array B has the same number of elements, and the base address of array A is at 0x10010004, how many memory read access cache hits in total are there?

[3 marks]

Parts (f) and (g) on the next page...

[1 mark]

Parts (f) and (g) are on a direct-mapped **instruction cache** with a capacity of 8 words with **each block containing 4 words**. Assume that Inst1 is at address **0x001F FFC4**.

(f) How many bits are there in the index field?

[1 mark]

(g) Assuming that array A has **100** elements and array B has the same number of elements. All elements in array A have the value 99. How many cache hits in the instruction cache in total are there? [3 marks]

=== END OF PAPER ===

| M     | IDC             | _           |       | ①<br>ence Data                                                               |         |                       | ARITHME                | ETIC CO          | RE INS  | TRU     | CTION SE                                            | т                            | (                                                | <u> </u>   | OPCO<br>/ FMT  |

|-------|-----------------|-------------|-------|------------------------------------------------------------------------------|---------|-----------------------|------------------------|------------------|---------|---------|-----------------------------------------------------|------------------------------|--------------------------------------------------|------------|----------------|

|       | ] ]             | Ref         | fer   | ence Data                                                                    | 8       |                       |                        |                  |         | FOR-    |                                                     |                              |                                                  |            | /FUN           |

|       |                 |             |       |                                                                              |         |                       | NAME,<br>Branch On     | MNEMO            |         |         |                                                     | OPERATIO                     |                                                  | - 10       | (He:<br>11/8   |

| COF   | RE INSTRUCTI    |             |       |                                                                              |         | OPCODE                | Branch On<br>Branch On |                  |         |         | if(FPcond)<br>if(!FPcond)                           |                              |                                                  |            |                |

| N     | AME, MNEMO      |             | FOR   |                                                                              |         | /FUNCT                | Divide                 | i i i i alac     | div     | _       | Lo=R[rs]/R                                          |                              |                                                  | ur (4)     | 0//-           |

|       | AME, MINEMO     |             |       | · ·                                                                          |         | (Hex)                 | Divide Un:             | signed           | divu    |         | Lo=R[rs]/R                                          |                              |                                                  | (6)        | 0//-           |

| Add   |                 | add         |       | R[rd] = R[rs] + R[rt]                                                        |         | 0/20 <sub>hex</sub>   | FP Add Sir             | nele             | add.s   | FR      | FIfd 1= FIfe                                        | 1 + F(ff)                    |                                                  |            | 11/10          |

|       | Immediate       | addi        | 1     | R[rt] = R[rs] + SignExtImm                                                   | (1,2)   |                       | FP Add                 | -                | add d   | FP      | {F[fd],F[fd                                         | +1]} = {F[f                  | s],F[fs+1]}                                      | +          | 11/11          |

| Add   | Imm. Unsigned   | addiu       | 1     | R[rt] = R[rs] + SignExtImm                                                   | (2)     | 9 <sub>hex</sub>      | Double                 |                  |         |         |                                                     | {r[                          | սյելս+լթ                                         |            |                |

| Add   | Unsigned        | addu        | R     | R[rd] = R[rs] + R[rt]                                                        |         | 0/21 <sub>hex</sub>   |                        |                  | c.r.s*  | FR      | FPcond = (                                          | F[fs] op F[f                 | LD?1:0                                           |            | 11/10          |

| And   |                 | and         | R     | R[rd] = R[rs] & R[rt]                                                        |         | 0/24 <sub>hex</sub>   | FP Compa<br>Double     | re               | c.r.d*  | FR      | FPcond = (                                          | {F[ft],F[fs+<br>{F[ft],F[ft+ | -1]} <i>op</i><br>-1]}21+0                       |            | 11/11          |

| And   | Immediate       | and1        | I     | R[rt] = R[rs] & ZeroExtImm                                                   | (3)     |                       |                        | eg. 11. 0        | r 1e) ( | oo is - | _, <, or <=                                         |                              |                                                  | ,          |                |

| -     |                 |             |       | if(R[rs]=R[rt])                                                              |         |                       | FP Divide              | Single           | div.s   | FR      | F[fd] = F[fs]                                       | 1/Ffft1                      |                                                  |            | 11/10          |

| Bran  | ch On Equal     | beq         | I     | PC=PC+4+BranchAddr                                                           | (4)     | 4 <sub>bex</sub>      | FP Divide              |                  | div d   | FR      | {F[fd],F[fd                                         | +1]} = {F[f                  | s],F[fs+1]}                                      | 1          | 11/11          |

| Deen  | ah On Mat Eaus  |             |       | if(R[rs]!=R[rt])                                                             |         | 5.                    | Double                 |                  |         |         |                                                     | {F[                          | ft],F[ft+1]}                                     |            |                |

| Bran  | ch On Not Equa  | Dne         | I     | PC=PC+4+BranchAddr                                                           | (4)     | 5 <sub>hex</sub>      |                        | y Single         | mul.s   | FR      | $\mathbf{F}[\mathbf{fd}] = \mathbf{F}[\mathbf{fd}]$ | s] * F[N]                    |                                                  |            | 11/10          |

| Jump  | ,               | 3           | J     | PC=JumpAddr                                                                  | (5)     | 2 <sub>bex</sub>      | FP Multipl             | y                | mul.d   | FR      | {F[fd],F[fd                                         | +1]} = {F[f                  | s],F[fs+1]}                                      | *          | 11/11          |

| Jum   | And Link        | jal         | J     | R[31]=PC+8;PC=JumpAddr                                                       | (5)     | 3 <sub>bex</sub>      | Double<br>FP Subtrac   |                  |         |         | F[fd]=F[fs]                                         | {r[                          | ft],F[ft+1]}                                     |            | 11/10          |

| -     | Register        | jr          |       | PC=R[rs]                                                                     |         | 0 / 08 <sub>hex</sub> | FP Subtrac             |                  | aw. 8   | I K     | F[fd]=F[fs]<br>{F[fd],F[fd                          | - r[n]<br>+1]} = {Fff        | sl.Fffs+113                                      | -          |                |

| -     | -               | -           |       | R[rt]={24*b0,M[R]rs]                                                         |         |                       | Double                 |                  | sub.d   | FR      | (a frolla fro                                       | (F)                          | ft],F[ft+1]}                                     | -          | 11/11          |

| Load  | Byte Unsigned   | 1bu         | I     | +SignExtImm](7:0)}                                                           | (2)     | 24 <sub>hex</sub>     | Load FP Si             | ingle            | lwc1    | I       | F[rt]=M[R]                                          |                              |                                                  |            | 31//           |

| Load  | Halfword        |             | -     | R[rt]={16'b0,M[R[rs]                                                         | ()      | 25                    | Load FP                |                  | 1dc1    | т       | F[rt]=M[R                                           |                              |                                                  | (2)        | 35//           |

|       | Unsigned        | lhu         | I     | +SignExtImm](15:0)}                                                          | (2)     | 25 <sub>hex</sub>     | Double                 |                  |         | -       | F[rt+1]=M                                           | R[rs]+Sign                   | ExtImm+4                                         |            |                |

| Load  | Linked          | 11          | I     | R[rt] = M[R[rs]+SignExtImm]                                                  | (2,7)   | 30bex                 | Move From              |                  | mfh1    |         | R[rd] = Hi                                          |                              |                                                  |            | 0//-           |

|       | Upper Imm.      | 1u1         | I     | R[rt] = {imm, 16'b0}                                                         | (-1-)   | fbex                  | Move From              |                  | mf10    |         | R[rd] = Lo                                          | r1                           |                                                  |            | 0//-           |

|       | Word            |             |       | ••••                                                                         | 0       |                       | Move From<br>Multiply  | n Control        | mult    |         | R[rd] = CR<br>{Hi,Lo} = 1                           |                              | a                                                |            | 10 /0.<br>0//- |

|       | word            | 1W          | I     | R[rt] = M[R[rs]+SignExtImm]                                                  | (2)     |                       | Multiply U             | Insigned         |         |         | $\{Hi,Lo\} = 1$<br>$\{Hi,Lo\} = 1$                  |                              | -                                                | ക          | 0/_/-          |

| Nor   |                 | nor         |       | $R[rd] = \sim (R[rs]   R[rt])$                                               |         | 0/27 <sub>hex</sub>   | Shift Right            | -                | sra     |         | R[rd] = R[r                                         |                              |                                                  | (0)        | 0/-            |

| Or    |                 | or          | R     | R[rd] = R[rs]   R[rt]                                                        |         | 0/25 <sub>hex</sub>   | Store FP S             |                  | swc1    |         | M[R[rs]   Si                                        |                              |                                                  | (2)        | 39//           |

| Or In | nmediate        | ori         | I     | R[rt] = R[rs]   ZeroExtImm                                                   | (3)     | dbex                  | Store FP               | -                | sdc1    | т       | M[R[rs]+Si                                          | gnExtImm]                    | = F[rt];                                         | (2)        | 3d//           |

| Set L | ess Than        | slt         | R     | R[rd] = (R[rs] < R[rt]) ? 1 : 0                                              |         | 0 / 2a <sub>bex</sub> | Double                 |                  | suci    |         | M[R[rs]+S                                           | gnExtImm                     | +4] = F[rt+                                      | 1]         | 5 <b>W</b>     |

| Set L | ess Than Imm.   | slt1        | 1     | R[rt] = (R[rs] < SignExtImm)? 1                                              | : 0 (2) | a <sub>hex</sub>      | FLOATING               | G-POINT          | INST    | RUCT    | ION FOR                                             | ATS                          |                                                  |            |                |

| Set L | ess Than Imm.   |             |       | R[rt] = (R[rs] < SignExtImm)                                                 |         |                       | FR                     | opcode           | _       | mt      | ft                                                  | fs                           | fd                                               |            | fun            |

|       | Unsigned        | sltiu       | I     | ?1:0                                                                         | (2,6)   | Dhex                  | rn L                   |                  | 26 25   |         |                                                     | 16 15                        | 11 10                                            | 65         | 1411           |

| Set L | ess Than Unsig. | sltu        | R     | R[rd] = (R[rs] < R[rt]) ? 1 : 0                                              | (6)     | 0 / 2b <sub>hex</sub> | Г                      | opcode           | _       | int     | n                                                   |                              | immed                                            |            |                |

| Shift | Left Logical    | <b>s</b> 11 | R     | R[rd] = R[rt] << shamt                                                       |         | 0 / 00 <sub>hex</sub> | · · _ 3                | -                | 26 25   |         | 1 20                                                | 16 15                        | mmov                                             | nuc        |                |

|       | Right Logical   | srl         | R     | R[rd] = R[rt] >> shamt                                                       |         | 0 / 02 <sub>hex</sub> | -                      | -                |         |         |                                                     |                              |                                                  |            |                |

| SIIII | Kight Logical   | SLI         | ĸ     |                                                                              |         | o / oznex             | PSEUDOI                | NSTRUG           |         | SET     | MNEMO                                               | JIC .                        | OPERA                                            | TION       | т              |

| Store | e Byte          | sb          | I     | M[R[rs]+SignExtImm](7:0) = R[rt](7:0)                                        | (2)     | 28hex                 | Branch                 | h Less Th        |         |         | blt                                                 |                              | <r[rt]) pc<="" td=""><td></td><td></td></r[rt])> |            |                |

|       | -               |             |       | M[R[rs]+SignExtImm] = R[rt];                                                 | (4)     |                       |                        | h Greater        |         |         | bqt                                                 |                              | <r[n]) pc<="" td=""><td></td><td></td></r[n])>   |            |                |

| Store | e Conditional   | SC          | 1     | R[rt] = (atomic)?1:0                                                         | (2,7)   | 38hex                 | Branch                 | h Less Th        | an or E |         | ble                                                 | if(R[rs]                     | <=R[rt]) P                                       | C = L      | abel           |

| C1    | Halfurg-d       |             |       | M[R[rs]+SignExtImm](15:0) =                                                  |         | 20.                   |                        | h Greater        |         | Equa    |                                                     |                              | >=R[n]) P                                        |            | abel           |

| Store | Halfword        | sh          | 1     | R[rt](15:0)                                                                  | (2)     | 29 <sub>hex</sub>     | Load I<br>Move         | mmediate         | e       |         | 11                                                  |                              | immediate<br>P[m]                                | •          |                |

| Store | Word            | SW          | I     | M[R[rs]+SignExtImm] = R[rt]                                                  | (2)     | 2b <sub>hex</sub>     |                        |                  |         |         | move                                                | R[rd] =                      |                                                  |            |                |

| Subt  | ract            | sub         | R     | R[rd] = R[rs] - R[rt]                                                        | 0       | 0/22 <sub>hex</sub>   | REGISTE                | R NAME           | , NUM   | BER,    | USE, CAL                                            | L CONVE                      |                                                  |            |                |

|       | ract Unsigned   | subu        |       | R[rd] = R[rs] - R[rt]                                                        | /       | 0/23hex               | NA                     | ME NU            | MBER    |         | USE                                                 |                              | PRESER                                           |            |                |

| Such  | Cost Choighed   |             |       | se overflow exception                                                        |         | nex                   |                        |                  | 0       |         | Constant Va                                         |                              |                                                  | CALI       |                |

|       |                 | (2) Sig     | nExtl | mm = { 16{immediate[15]}, imm                                                | ediate  | }                     |                        | ero<br>at        | 1       |         | embler Tem                                          |                              |                                                  | N.A.<br>No |                |

|       |                 | (3) Zer     | oExtl | Imm = { 16{1b'0}, immediate }                                                |         | -                     |                        |                  |         |         | es for Func                                         | *                            |                                                  |            |                |

|       |                 |             |       | ddr = { 14{immediate[15]}, immediate[15]},                                   |         | 2°60}                 | \$v0-                  | -\$v1            | 2-3     |         | Expression                                          |                              |                                                  | No         |                |

|       |                 |             |       | <pre>dr = { PC+4[31:28], address, 2't s considered unsigned numbers (v</pre> |         | 0000                  | \$a0-                  | - <b>S</b> a3    | 4-7     |         | iments                                              |                              |                                                  | No         |                |

|       |                 |             |       | s considered unsigned numbers (v<br>est&set pair; R[rt] = 1 if pair atom     |         |                       | \$10                   | -                | 8-15    | ~       | poraries                                            |                              |                                                  | No         |                |

| DAC   | IC INSTRUCTI    |             |       | • • • •                                                                      |         |                       | \$s0                   | -                | 6-23    |         | ed Temporal                                         | ies                          |                                                  | Yes        |                |

|       |                 | _           |       |                                                                              |         | A                     | \$18                   |                  | 24-25   |         | poraries                                            |                              |                                                  | No         |                |

|       | R opcode        | ſ           |       | rt rd sham                                                                   |         | funct                 | \$k0                   | - <b>\$</b> k1 2 | 26-27   | Rese    | erved for OS                                        | Kernel                       |                                                  | No         |                |

|       |                 | 26 25       |       | 20 16 15 11 10                                                               | 65      |                       | \$                     | gp               | 28      | Glot    | oal Pointer                                         |                              |                                                  | Yes        |                |

|       | I opcode        | Г           |       | rt immed                                                                     | nate    |                       | \$                     | sp               | 29      | Stac    | k Pointer                                           |                              |                                                  | Yes        |                |

|       | 31 2            | 6 25        | 21    | 20 16 15<br>address                                                          |         |                       | \$                     | ſp               | 30      | Fran    | ne Pointer                                          |                              |                                                  | Yes        |                |

|       | J opcode        |             |       |                                                                              |         |                       |                        |                  | 31      | Retu    |                                                     |                              |                                                  | No         |                |