Design, Automation and Test in Europe Conference (DATE 2024)

# Prime+Reset: Introducing A Novel Cross-World Covert-Channel Through Comprehensive Security Analysis on ARM TrustZone

Yun Chen\*

National University of Singapore

Arash Pashrashid\*

National University of Singapore

Huawei Research Center

Yongzheng Wu Huawei Research Center Trevor E. Carlson

National University of Singapore

<sup>\*</sup> Equal Contribution

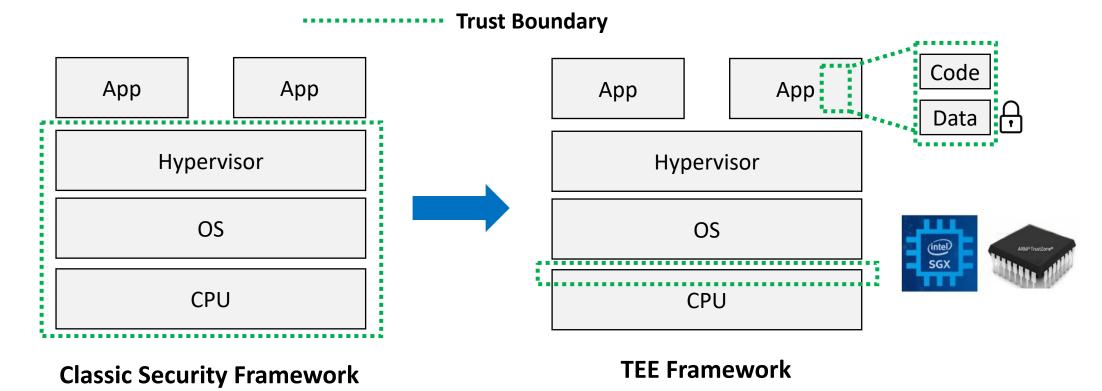

## **Trusted Execution Environments**

**Applications:**

Biometric Authentication

Electronic Payments

Digital Rights Management

# TrustZone TEE Architecture and Its Limitations

#### **Limitations and Problems:**

- TEEs are still vulnerable to various microarchitectural side channel attacks

- Lack of comprehensive microarchitectural security analysis of TrustZone

#### **Prior Works:**

Limited scope: Only considering cache and PMUs as a source of leakage

### **Motivation:**

- A comprehensive side/covert-channel vulnerability analysis on TrustZone

- Detecting a new leakage source

# Leakage Analysis Criteria

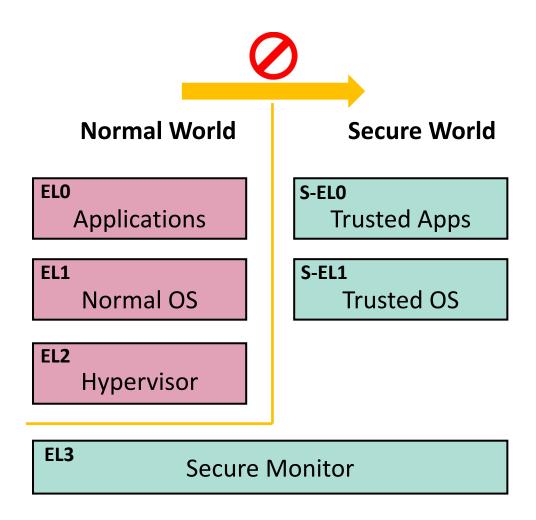

**Question**: Are components of an OoO processor isolated between the Secure World and the Normal World?

Requirements for a successful side/covert channel:

### RQ1

Shared resources among different execution domains that can create resource contention and execution footprints (e.g., cache)

### RQ2

Microarchitectural events that can create distinguishable and leaking events during execution (e.g., out-of-order execution)

### Analysis result:

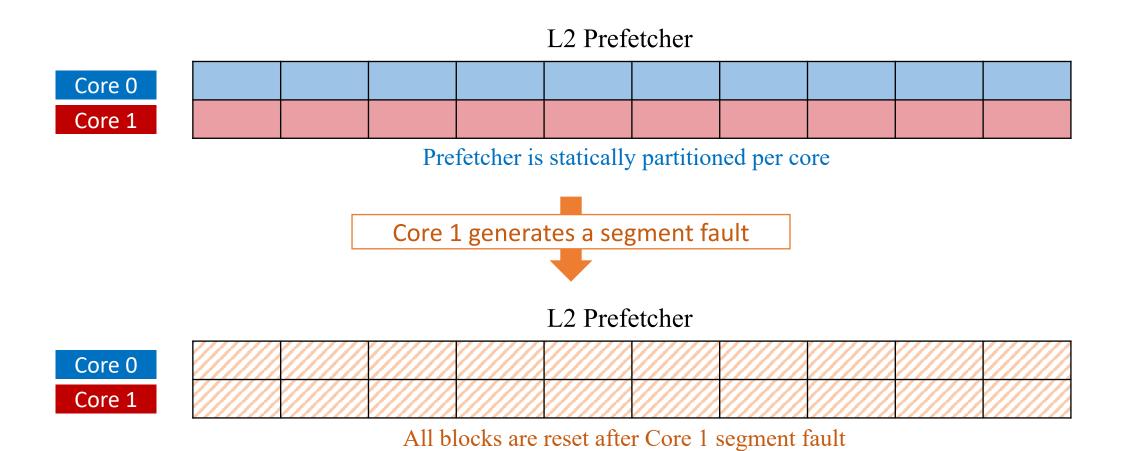

| Component | <b>Issue Ports</b> | TLB               | L1 Prefetcher         | L1 Cache              | L2 Prefetcher            |

|-----------|--------------------|-------------------|-----------------------|-----------------------|--------------------------|

| Leakage?  | No                 | No                | No                    | No                    | Yes                      |

| Reason    | Pipeline flushing  | Pipeline flushing | Entry<br>invalidating | Entry<br>invalidating | Resetting between worlds |

## Our Observation from L2 Prefetcher

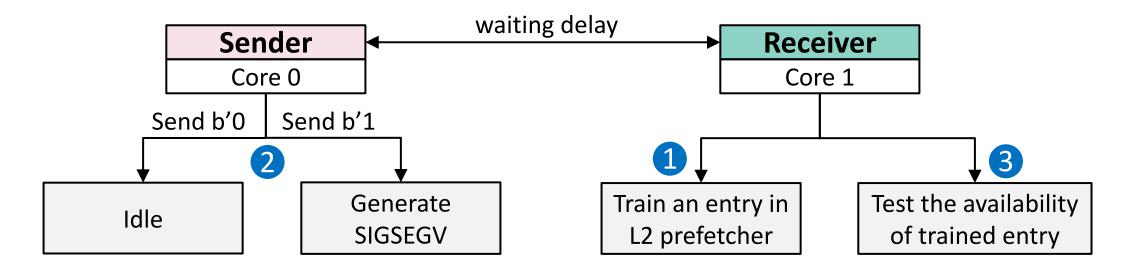

# PRIME+RESET: Covert-Channel using the L2 Prefetcher

| Attack                   | <b>Error Rate</b> | Max Throughput |

|--------------------------|-------------------|----------------|

| Prime+Count <sup>1</sup> | <2%               | ~ 1 Kib/s      |

| μarch-Count <sup>2</sup> | <2%               | 12 Kib/s       |

| PRIME+RESET (ours)       | <2%               | 776 Kib/s      |