Bahurupi: Polymorphic Heterogeneous Multi-Core

Computing systems have made an irreversible transition towards parallel architectures with the multi-cores and many cores.

However, power and thermal limits are rapidly bringing the computing community to another crossroad where a chip can have

many cores but a significant fraction of them are left unpowered --- or dark --- at any point in time. This phenomenon,

known as dark silicon, is driving the emergence of heterogeneous platforms consisting of cores with diverse power-performance

characteristics enabling better match between application requirements and computation capabilities leading to substantially

improved energy-efficiency.

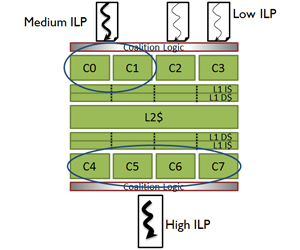

This project aim to design a polymorphic heterogeneous multi-core architecture, called Bahurupi, which can be tailored according to

the application by software. Bahurupi is designed and fabricated as a homogeneous multi-core system containing multiple identical

(simple) cores on chip along with some amount of reconfigurable logic. The main novelty of Bahurupi lies in its highly flexible

architecture. Post-fabrication, software can configure or compose together primitive cores to create a customized multi-core system that best matches the

needs of a specific application. Moreover, the functionality of the cores can be extended, again at runtime, through application-specific custom instructions

implemented in the reconfigurable fabric on-chip. This software directed re-configurability allows us to enjoy the power-performance benefits of a

customized and optimized heterogeneous multi-core system without paying the hefty price of design and fabrication for customization.

People:

- Tulika Mitra

- Mihai Pricopi

- Chen Liang

- Zhong Guwanen

- Ijaz Ahmad

- Thomas Marconi

- Kalindu Herath

Collaborator:

- Sri Parameswaran, University of New South Wales

- Philip Brisk, University of California, Riverside

- Smail Niar, University of Valenciennes and Hainaut-Cambresis

Representative Publications:

[DAC] Hierarchical Power Management for Asymmetric Multi-Core in Dark Silicon Era

Thannirmalai Somu Muthukaruppan, Mihai Pricopi, V Vanchinathan, Tulika Mitra, Sanjay Vishin

50th Design Automation Conference, June 2013

[FPT]

Graph Minor Approach for Application Mapping on CGRAs

Liang Chen, Tulika Mitra

International Conference on Field Programmable Technology, December 2012

Best Paper Award

[TACO]

Bahurupi: A polymorphic heterogeneous multi-core architecture

![]()

Mihai Pricopi, Tulika Mitra

ACM Transactions on Architecture and Code Optimization, 8(4), January 2012

Presented at 7th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC) 2012

Best Student Poster Award

[DAC]

Shared Reconfigurable Fabric for Multi-Core Customization<

Liang Chen, Tulika Mitra

Design Automation Conference, June 2011

An Efficient Framework for Dynamic Reconfiguration of Instruction-Set Customization

Huynh Phung Huynh, Edward Sim, Tulika Mitra

Design Automation for Embedded Systems, Springer Journal, 13(1-2), June 2009

Invited: Special Issue on Best Papers from ESWeek 2007

[FPL] Disjoint Pattern Enumeration for Custom Instructions Identification [Technical report]

Pan Yu, Tulika Mitra

International Conference on Field Programmable Logic and Applications, August 2007

Best Paper Award Nomination

[CASES]

Scalable Custom Instructions Identification for Instruction-Set Extensible Processors,

Pan Yu, Tulika Mitra

International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, September 2004

[DAC]

Characterizing Embedded Applications for Instruction-Set Extensible Processors

Pan Yu, Tulika Mitra

Design Automation Conference, June 2004

Funding:

- Bahurupi : Polymorphic Heterogeneous Multi-Core Systems. Academic Research Council Tier 2 Fund, Ministry of Education, 2009-2013

- Computation Model for 3D Multi-Core Systems. NUS Faculty Research Committee (FRC) Academic Research Fund, 2012-2015

- NSF East Asia and Pacific Summer Institutes Programme (EAPSI) 2012

- High-level specification, compiling, and synthesis of MP-RASIP. Merlion PhD project, 2013-2015