Memory Stage

Requirements

Only the load/store instructions need to perform operation in this stage. As for other instructions, this stage will not do anything. We will use the memory address calculated by the ALU stage.

-

Read calculated address from ALU stage and data to be stored (if any) from decode stage).

-

Read from memory or write to memory (never both).

-

Either the data read from memory or calculated from ALU stage will be passed to the next stage (i.e., writeback stage).

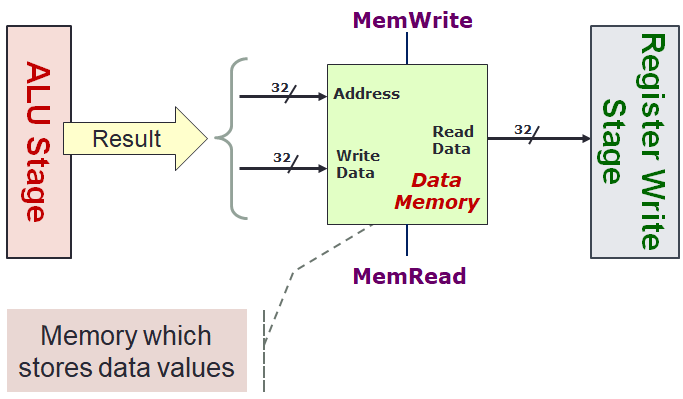

Block Diagram

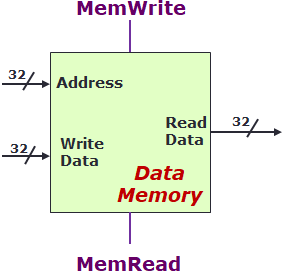

Again, it is rather straightforward because most of the work is done by the Data Memory.

This will be explained on the second half of the semester.

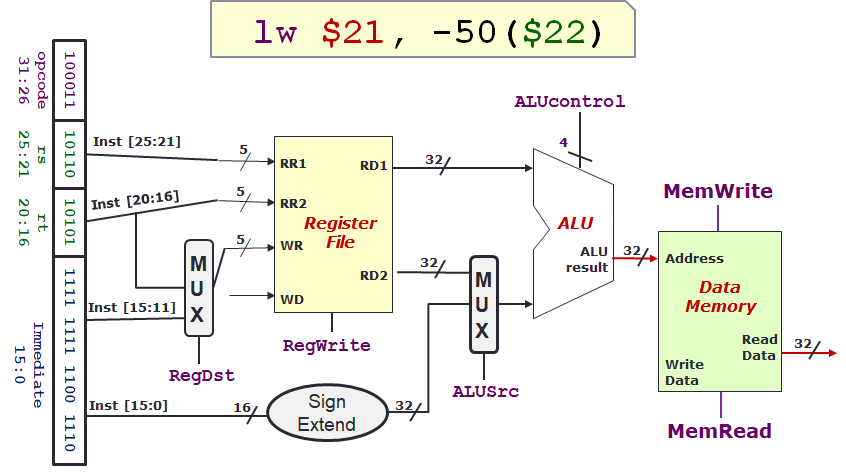

Load

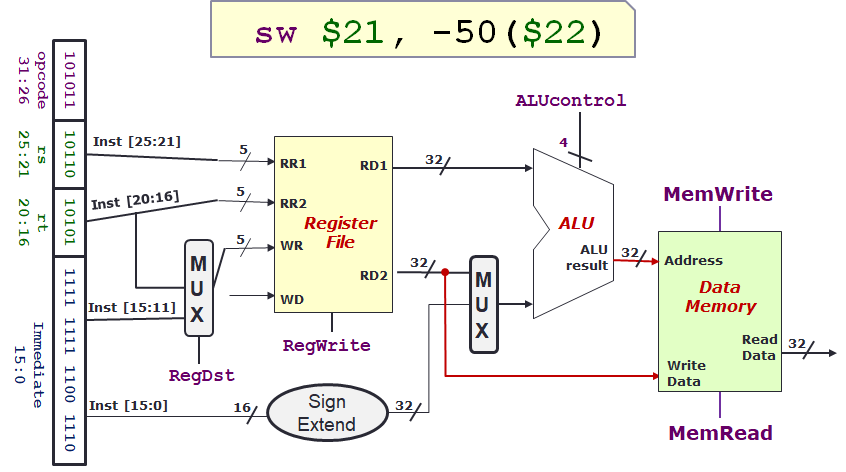

Store

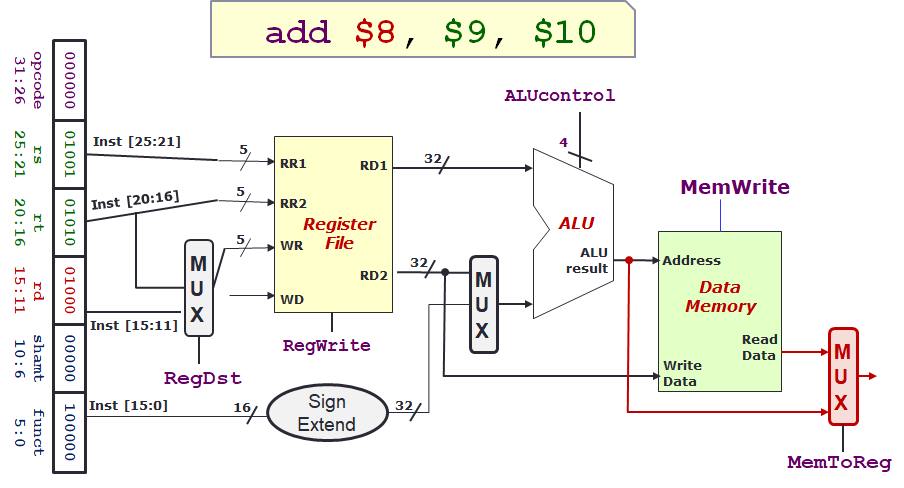

Non-Memory

MemToReg Multiplexer

The MemToReg multiplexer is inverted.

In particular:

Read Data:1ALU result:0

Elements

Data Memory

Data Memory is a storage element for the data similar to Instruction Memory.

However, unlike Instruction Memory, we have two control signals to determine whether we will write to memory, read from memory or neither.

Note that we will not both read and write at the same time.

| Functional Conceptual View of Data Memory | |

|---|---|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 | |